### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2017-191964 (P2017-191964A)

(43) 公開日 平成29年10月19日(2017.10.19)

| (51) Int.Cl. |      |            | F 1  |      |   | テーマコード (参考) |

|--------------|------|------------|------|------|---|-------------|

| нозм         | 1/10 | (2006.01)  | нозм | 1/10 | Α | 5 J O 2 2   |

| нозм         | 1/36 | (2006.01)  | нозм | 1/36 |   |             |

| нозм         | 1/14 | (2006, 01) | нозм | 1/14 | Α |             |

|                       |                                                      | 審査請求     | 未請求                                      | 請求項             | の数 2         | ΟL           | 全(           | 10 頁) |  |  |

|-----------------------|------------------------------------------------------|----------|------------------------------------------|-----------------|--------------|--------------|--------------|-------|--|--|

| (21) 出願番号<br>(22) 出願日 | 特願2016-78798 (P2016-78798)<br>平成28年4月11日 (2016.4.11) | (71) 出願人 | 000003193<br>凸版印刷株式会社<br>東京都台東区台東1丁目5番1号 |                 |              |              |              |       |  |  |

|                       |                                                      | (72) 発明者 | 河内 周平<br>東京都台東区台東1丁目5番1号 凸版印             |                 |              |              |              | 凸版印   |  |  |

|                       |                                                      | (72) 発明者 | 刷株式会社内<br>瀬戸 健二<br>東京都台東区台東1丁目5番1号 凸版印   |                 |              |              |              |       |  |  |

|                       |                                                      |          | 刷株式会社内                                   |                 |              |              |              |       |  |  |

|                       |                                                      | Fターム (参  | 考) 5J02                                  | 22 AA06<br>CD03 | AA14<br>CD04 | BA01<br>CF01 | BA07<br>CF07 | CB02  |  |  |

|                       |                                                      |          |                                          |                 |              |              |              |       |  |  |

|                       |                                                      |          |                                          |                 |              |              |              |       |  |  |

## (54) 【発明の名称】 A D変換回路

### (57)【要約】

【課題】本発明は、従来のオフセットを有し応答速度の遅いコンパレータを用い、そのため消費電流を抑えることができる、精度の向上したAD変換回路を提供する。 【解決手段】入力電圧を上位ビット用基準電圧と比較した結果に基づき仮上位ビット電圧信号を作成する仮上位ビット電圧信号を作成する仮上位ビット電圧信号を比較する高精度コンパレータ回路を有し、前記高精度コンパレータ回路の出力に基づき上位ビットディジタルデータを補正して作成する上位ビットディジタルデータを補正して作成する上位ビットディジタルデータに係わる下位ビット用基準電圧を選択する下位ビット用基準電圧と比較して下位ビットディジタルデータを作成する。

### 【選択図】図1

#### 【特許請求の範囲】

### 【請求項1】

入力電圧を上位ビット用基準電圧と比較した結果に基づき仮上位ビット電圧信号を作成 する仮上位ビット電圧選択回路と、前記入力電圧と前記仮上位ビット電圧信号を比較する 高精度コンパレータ回路を有し、

前 記 高 精 度 コ ン パ レ ー タ 回 路 の 出 力 に 基 づ き 上 位 ビ ッ ト デ ィ ジ タ ル デ ー タ を 補 正 し て 作 成 する上位ビットディジタルデータ補正エンコード回路を有し、

前記上位ビットディジタルデータに係わる下位ビット用基準電圧を選択する下位ビット用 基準電圧選択スイッチ群を有し、

前 記 入 力 電 圧 を 前 記 下 位 ビ ッ ト 用 基 準 電 圧 と 比 較 し て 下 位 ビ ッ ト デ ィ ジ タ ル デ ー タ を 作 成 する下位ビットディジタルデータ作成回路を有することを特徴とするAD変換回路。

#### 【請求項2】

請求項1記載のAD変換回路であって、前記入力電圧の入力端子と前記上位ビット用基 準電圧の入力端子にバッファ回路を備えた上位ビット用低精度コンパレータ群回路を用い て前記入力電圧を前記上位ビット用基準電圧と比較することを特徴とするAD変換回路。

#### 【発明の詳細な説明】

## 【技術分野】

#### [00001]

本発明は、アナログ信号をディジタル信号に変換して出力するAD変換回路に関する。

### 【背景技術】

#### [00002]

近 年 、 デ ィ ジ タ ル 電 気 製 品 で は 、 例 え ば 画 像 処 理 の 高 精 細 化 が 進 ん で お り 、 A D 変 換 回 路の高解像化、高ビット化、高速化が求められている。また、例えばセンサのアナログフ ロントエンドで使用されるAD変換回路などでは、さらに低消費電力が求められている。 このような高解像化、高ビット化、高速化の要求に対し、従来のAD変換回路では対応が 出来難くなっている。

#### [00003]

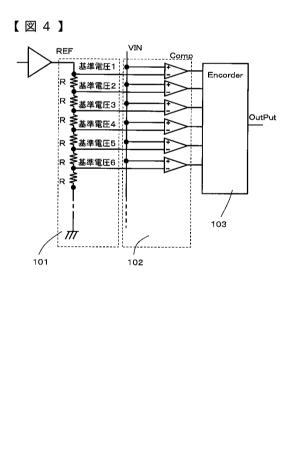

図4は従来の並列型AD変換回路の一例である。抵抗Rを直列接続したラダー抵抗10 1と、ラダー抵抗101より出力される基準電圧と入力電圧VINとを比較して高低電圧 を出力するコンパレータ群回路102と、コンパレータ群回路102の出力からディジタ ル量に変換して出力するエンコード回路103と、から形成されている。ラダー抵抗10 1 にはオペアンプより出力されるリファレンス電圧REFが印加され、各抵抗間から、基 準電圧が出力される。入力電圧は、変換の対象であるアナログ信号である。

#### [0004]

入力電圧に対し、それより低い基準電圧が接続されているコンパレータは、全て高電圧 が出力される。それ以上の基準電圧が接続されているコンパレータは低電圧が出力される 。このようなコンパレータの出力に対し、エンコード回路103で符号化され、ディジタ ル信号が出力される。並列型AD変換回路は入力電圧VINに対し、クロックで同時に各 ビットが出力されるので、高速AD変換に有利である。

### 【先行技術文献】

## 【特許文献】

#### [0005]

【特許文献 1 】特開 2 0 1 1 - 1 9 3 3 4 0 号公報

## 【発明の概要】

【発明が解決しようとする課題】

## [0006]

しかし、このようなAD変換回路の精度を向上させるには、特許文献1のように、コン パレータの精度を良くしなければならない。また、応答速度やオフセットにより誤判定が 起きてしまうことも阻害要因である。そしてオフセットを抑えるため、また応答速度を速 めるためにコンパレータの面積を広くすると全体の面積が増加し、さらに電流が増加し消 10

20

30

40

費電力が増えてしまうという問題が起こる。 n ビット符号の信号では、 2 n - 1 個のコンパレータが必要とされる。

#### [0007]

本発明は、従来のオフセットを有し、応答速度の遅いコンパレータを用いることで、消費電流を抑えることができ、かつ精度の向上した A D 変換回路を提供することを課題とする。

#### 【課題を解決するための手段】

### [0008]

本発明は上記の課題を解決するために、入力電圧を上位ビット用基準電圧と比較した結果に基づき仮上位ビット電圧信号を作成する仮上位ビット電圧選択回路と、前記入力電圧と前記仮上位ビット電圧信号を比較する高精度コンパレータ回路を有し、

前記高精度コンパレータ回路の出力に基づき上位ビットディジタルデータを補正して作成 する上位ビットディジタルデータ補正エンコード回路を有し、

前記上位ビットディジタルデータに係わる下位ビット用基準電圧を選択する下位ビット用 基準電圧選択スイッチ群を有し、

前記入力電圧を前記下位ビット用基準電圧と比較して下位ビットディジタルデータを作成する下位ビットディジタルデータ作成回路を有することを特徴とするAD変換回路である

### [0009]

本発明は、これにより、従来の仕様のサイズ、従来のオフセットを有する上位ビット用低精度コンパレータを用い、従ってコンパレータの面積が削減でき、応答速度が遅くても良く、そのため消費電流を抑えることができる、精度の向上したAD変換回路とすることができる効果がある。

#### [0010]

また、本発明は、上記の A D 変換回路であって、前記入力電圧の入力端子と前記上位ビット用基準電圧の入力端子にバッファ回路を備えた上位ビット用低精度コンパレータ群回路を用いて前記入力電圧を前記上位ビット用基準電圧と比較することを特徴とする A D 変換回路である。

### 【発明の効果】

## [0011]

本発明の A D 変換回路は、以上のような構成であるので、使用すべき高精度のコンパレータは、上位ビット用の 1 つのみで済む。また、ラダーに接続される低精度コンパレータは高精度を必要としないため、面積が小さく応答速度が遅い低精度コンパレータを用いることができる。

### [ 0 0 1 2 ]

すなわち、本発明によれば、精度が高く応答速度が速いAD変換回路でありながら、従来の仕様のサイズ、従来のオフセットを有するコンパレータを用いることができ、コンパレータの消費電力を抑え、製造コストも低減できるAD変換回路が得られる効果がある。

## 【図面の簡単な説明】

### [0013]

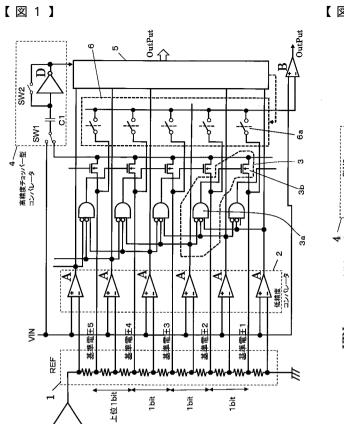

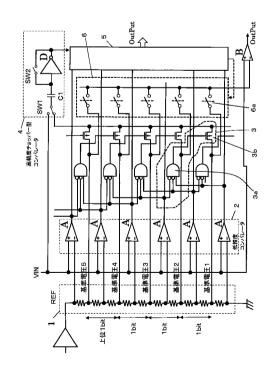

【図1】本発明の第1の実施形態の高精度上位ビットディジタルデータ作成回路を備えたAD変換回路をあらわす回路図である。

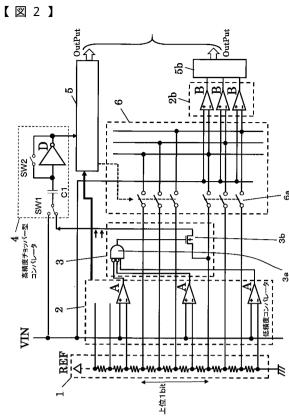

【図2】本発明の第2の実施形態の高精度上位ビットディジタルデータ作成回路を備えたAD変換回路をあらわす回路図である。

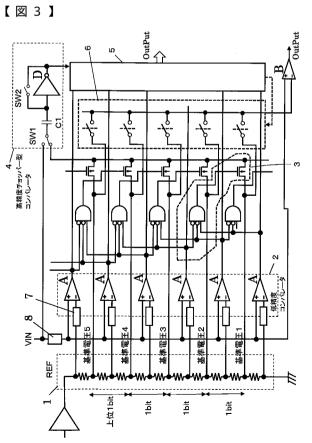

【図3】本発明の第3の実施形態の高精度上位ビットディジタルデータ作成回路を備えたAD変換回路をあらわす回路図である。

【図4】従来の並列型AD変換回路を示す回路図である。

### 【発明を実施するための形態】

### [ 0 0 1 4 ]

<第1の実施形態>

20

10

30

40

以下本発明の第1の実施形態について図1を参照して説明する。図1は、本発明のAD 変換回路の第1の実施形態における高精度上位ビットディジタルデータ作成回路と、1ビットの下位ビットディジタルデータ作成回路との全体回路をあらわす回路図である。

- [ 0 0 1 5 ]

- (1ビットの下位ビットディジタルデータ作成回路)

1 ビットの下位ビットディジタルデータ作成回路は、下位ビット用基準電圧選択スイッチ群 6 と、下位ビット用コンパレータ回路 B から成る。

[0016]

(下位ビット用基準電圧選択スイッチ群6)

下位ビット用基準電圧選択スイッチ群6は、上位ビットディジタルデータ補正エンコード回路5の出力データで制御され、下位ビット用基準電圧選択スイッチ群6は、上位ビットディジタルデータ補正エンコード回路5の出力データに係わる下位ビット用基準電圧を選択し、その下位ビット用基準電圧の信号を下位ビット用コンパレータ回路Bの一方の入力端子に接続する。

[0017]

下位ビット用コンパレータ回路Bの他方の入力端子には入力電圧VINを接続して、入力電圧VINと与えられた下位ビット用の基準電圧とを比較する。

[ 0 0 1 8 ]

(高精度上位ビットディジタルデータ作成回路)

高精度上位ビットディジタルデータ作成回路は、複数の抵抗素子を直列接続し複数の基準電圧を発生するラダー抵抗1と、上位ビット用低精度コンパレータAの群による上位ビット用低精度コンパレータ群回路2と、仮上位ビット電圧選択回路3と、高精度コンパレータ回路4と、上位ビットディジタルデータ補正エンコード回路5から成る。高精度コンパレータ回路4は、回路のオフセット電圧を小さくして精度の良い電圧比較をするオフセットキャンセル機能を有する

[0019]

(上位ビット用低精度コンパレータ群回路2)

図 1 のように、高精度上位ビットディジタルデータ作成回路は、ラダー抵抗 1 が発生した複数の基準電圧のうちの上位ビット用基準電圧と入力電圧 V I N を比較する上位ビット用低精度コンパレータ A の群から成る上位ビット用低精度コンパレータ群回路 2 を持つ。

[0020]

上位ビット用低精度コンパレータ群回路 2 の 2 値データの信号の出力端子は、仮上位ビット電圧選択回路 3 及び上位ビットディジタルデータ補正エンコード回路 5 の入力端子に接続する。

[0021]

(仮上位ビット電圧選択回路3)

1 つの仮上位ビット電圧選択回路3 毎に1 つの3 入力論理和回路3 a を備え、その3 入力論理和回路の各入力端子に、上位ビット用低精度コンパレータ群回路2 において隣り合う3 つの上位ビット用低精度コンパレータ A の出力端子を接続する。

[0022]

詳しくは、仮上位ビット電圧選択回路3に接続する3つの上位ビット用低精度コンパレータAの内の最下位の上位ビット用低精度コンパレータAの出力端子を3入力論理和回路3aの1つの入力端子に接続する。そして、その上位ビット用低精度コンパレータAより上位の2つの上位ビット用低精度コンパレータAの出力信号をインバータで反転した出力信号端子を3入力論理和回路3aの残りの入力端子に接続する。

[0023]

3 入力論理和回路 3 a はその 3 入力の論理和を取って出力端子から出力する。その出力端子は、その仮上位ビット電圧選択回路 3 毎の、仮上位ビット電圧信号出力スイッチ回路 3 b の制御端子に出力する。

[ 0 0 2 4 ]

50

10

20

30

10

20

30

40

50

ここで、ある3入力論理和回路3 a の 3 つの入力端子へ接続する3 つの上位ビット用低精度コンパレータA の出力信号が、下位の端子から順に(論理 '1')、(論理 '0')、(論理 '0')である場合に、その3入力論理和回路3 a が、仮上位ビット電圧信号出力スイッチ回路3 b の制御端子を制御して、仮上位ビット電圧信号出力スイッチ回路3 b に仮上位ビット電圧信号を出力させる。

#### [0025]

仮上位ビット電圧信号出力スイッチ回路 3 b は、 3 入力論理和回路 3 a の入力端子に接続する 3 つの低精度コンパレータ A の入力端子が接続する 3 つの基準電圧のうち、最下位の基準電圧の上の基準電圧を仮上位ビット電圧信号として出力し、その出力端子を高精度コンパレータ回路 4 の入力端子に接続する。

[0026]

(高精度コンパレータ回路4)

高精度コンパレータ回路 4 は、オフセットキャンセル機能を有する高精度チョッパー型コンパレータの回路に構成する。その高精度チョッパー型コンパレータにより、仮上位ビット電圧選択回路 3 から受け取った仮上位ビット電圧信号と入力電圧 V I N を比較し、比較結果の上位ビットディジタルデータの 1 ビット補正信号を上位ビットディジタルデータ補正エンコード回路 5 に出力する。

[0027]

(上位ビットディジタルデータ補正エンコード回路5)

上位ビットディジタルデータ補正エンコード回路 5 は、上位ビット用低精度コンパレータ群回路 2 の出力信号の 2 値データを作成する。詳しくは、高精度コンパレータ回路 4 (高精度チョッパー型コンパレータ)から受信した上位ビットディジタルデータの 1 ビット補正信号に基づき 1 ビット補正した正確な上位ビットディジタルデータを作成する。

[0028]

(高精度上位ビットディジタルデータ作成回路の動作)

以下で、高精度上位ビットディジタルデータ作成回路の動作を説明する。

[0029]

(仮上位ビット電圧選択回路3)

仮上位ビット電圧選択回路3の3入力論理和回路3aの3つの入力端子に、上位ビット 用低精度コンパレータ群回路2において隣り合う3つの上位ビット用低精度コンパレータ Aの出力端子を接続する。

[0030]

そして、仮上位ビット電圧選択回路3は、隣り合う3つの上位ビット用低精度コンパレータAのうちの最下位の上位ビット用低精度コンパレータAの出力電圧が高電圧(論理・1・)となっていて、その上に続く2つの上位ビット用低精度コンパレータAの出力が低電圧(論理・0・)となっている場合に、仮上位ビット電圧信号出力スイッチ回路3bに仮上位ビット電圧信号を出力させる。

[0031]

仮上位ビット電圧信号出力スイッチ回路3 b は、3 入力論理和回路3 a の入力端子に接続する3 つの低精度コンパレータ A の入力端子が接続する3 つの基準電圧のうち、最下位の基準電圧の上の基準電圧を仮上位ビット電圧信号として、高精度コンパレータ回路4 の入力端子に出力する。

[0032]

(高精度コンパレータ回路4)

高精度コンパレータ回路 4 は、オフセットキャンセル機能を有する高精度チョッパー型コンパレータの回路で構成する。その高精度チョッパー型コンパレータにより、仮上位ビット電圧選択回路 3 から受け取った仮上位ビット電圧信号と入力電圧 V I N を比較し、上位ビットディジタルデータの 1 ビット補正信号を出力する。

[ 0 0 3 3 ]

高精度チョッパー型コンパレータの回路構成の高精度コンパレータ回路4は、インバー

10

20

30

40

50

タDの入力側に、コンデンサC1を経由してスイッチSW1の出力端子を接続し、スイッチSW1の第1の入力端子は入力電圧VINに接続し、第2の入力端子は選択された仮上位ビット電圧信号に接続する。スイッチSW1により、コンデンサC1に、入力電圧VINと選択された仮上位ビット電圧信号を切り替えて接続する。またインバータDの入力を、スイッチSW2を経由してインバータDの出力端子に接続する。

### [0034]

このような高精度チョッパー型コンパレータの回路構成により、高精度コンパレータ回路4は、まず、スイッチSW2を接続し、スイッチSW1を入力電圧VIN側に接続し、コンデンサC1を入力電圧VIN(高精度コンパレータの閾値電圧を減じる)で充電しておく。この場合に、インバータDの入力には、閾値電位と、コンデンサを介して入力電圧VINとが直列に印加され、オフセットキャンセルがなされる。

[0035]

次に、スイッチSW2を切り、スイッチSW1を仮上位ビット電圧信号側に切り替える。そうすると、インバータDの入力には、コンデンサC1に充電された入力電圧VINと、仮上位ビット電圧信号・VINが印加される。

[0036]

高精度コンパレータ回路4(高精度チョッパー型コンパレータ)は、インバータDのオフセットが補償されて動作する。

[ 0 0 3 7 ]

そして、 が正の場合は、インバータDの出力が低電圧(論理' 0 ')になる。その出力信号を受け取った上位ビットディジタルデータ補正エンコード回路 5 が、上位ビット用低精度コンパレータ群回路 2 の出力信号の 2 値データから正規な上位ビットディジタルデータを作成して出力する。

[ 0 0 3 8 ]

一方、 が負の場合は、インバータDの出力が高電圧(論理' 1 ')になる。その出力信号を受け取った上位ビットディジタルデータ補正エンコード回路 5 は、上位ビット用低精度コンパレータ群回路 2 の出力信号の 2 値データを 1 ビット増したデータから正規な上位ビットディジタルデータを作成して出力する。

[0039]

このようにして、コンパレータ回路 2 の精度が低精度であっても、オフセットがキャンセルされた高精度コンパレータ回路 4 を用いることにより、正確に A D 変換した上位ビットディジタルデータが得られる。

[0040]

この高精度上位ビットディジタルデータ作成回路では、特に、上位ビット用低精度コンパレータAが、時間的に遅延が存在するので、最大の誤差を含む。そのため、先ず、上位ビット用低精度コンパレータ群回路2が、複数の基準電圧から、誤差を含んだ仮上位ビット電圧信号を選択し、仮の決定をしておく。

[0041]

次に、その仮上位ビット電圧信号を高精度コンパレータ回路 4 (高精度チョッパー型コンパレータ)で入力電圧 V I N と比較し、最小ビットに対応する基準電圧を正確に決定し、その結果に基づき上位ビットディジタルデータ補正エンコード回路 5 が 1 ビット補正した正確な上位ビットディジタルデータを作成して出力する。これにより、コンパレータの持つ誤差を含まない出力データを得ることができる。

[0042]

(1ビットの下位ビットディジタルデータ作成回路)

以下で、1ビット下位ビットディジタルデータ作成回路の動作を説明する。

[0043]

(基準電圧選択スイッチ)

図 1 の回路図のように、下位ビット用基準電圧選択スイッチ群 6 が、上位ビットディジタルデータ補正エンコード回路 5 が作成した高精度上位ビットディジタルデータで制御さ

10

20

30

40

50

れて下位ビット用コンパレータ回路Bに接続する下位ビット用基準電圧を選択して出力する。その出力端子を下位ビット用コンパレータ回路Bの入力端子に接続する。

### [0044]

詳しくは、下位ビット用基準電圧選択スイッチ群 6 が、上位ビットディジタルデータ補正エンコード回路 5 の出力する高精度上位ビットディジタルデータで制御されて下位ビット用基準電圧選択スイッチ 6 a を選択して回路を閉じることで、下位ビット用基準電圧を選択して下位ビット用コンパレータ回路 B の入力端子に接続する。

### [0045]

(下位ビット用コンパレータ回路 B)

下位ビット用コンパレータ回路 B のもう 1 つの入力端子に入力電圧 V I N を接続する。そして、下位ビット用コンパレータ回路 B の出力信号の 2 値データを、 1 ビットの下位ビットディジタルデータ作成回路の下位ビットディジタルデータとして出力する。

#### [0046]

こうして、上位ビットディジタルデータ補正エンコード回路 5 が出力した正確な上位ビットディジタルデータと、下位ビット用コンパレータ回路 B が出力した下位ビットディジタルデータとを合わせて、正確に A D 変換したディジタルデータを得ることができる。

#### [0047]

本実施形態は以上のような構成、および作用を有するから、低速仕様の小さい面積を持ち、低精度用のオフセットを有する低精度コンパレータを主な素子に用いることができるので、高速 A D 変換回路の集積回路の面積を削減できる効果がある。また、用いるコンパレータの応答速度が遅くても良いため、 A D 変換回路の消費電流を抑えることができる、高精度高速 A D 変換回路が得られる効果がある。

### [0048]

< 第 2 の 実 施 形 態 >

以下本発明の第2の実施形態について図2を参照して説明する。第2の実施形態のAD 変換回路は、図2の様に2ビットの下位ビットディジタルデータ作成回路を有する。それ 以外の回路は、第1の実施形態と同様に、ラダー抵抗1と高精度上位ビットディジタルデータ作成回路を有する。

### [0049]

(高精度上位ビットディジタルデータ作成回路)

高精度上位ビットディジタルデータ作成回路は、第1の実施形態と同様に構成し、同様に動作させる。

#### [0050]

(下位ビットディジタルデータ作成回路)

第2の実施形態の2ビットの下位ビットディジタルデータ作成回路は、下位ビット用基準電圧選択スイッチ群6と、下位ビット用コンパレータ回路Bの群による下位ビット用コンパレータ群回路2bと下位ビット用エンコード回路5bから構成する。

### [0051]

(下位ビット用基準電圧選択スイッチ群6)

下位ビット用基準電圧選択スイッチ群 6 は、上位ビットディジタルデータ補正エンコード回路 5 の出力データで制御される。下位ビット用基準電圧選択スイッチ群 6 は、上位ビットディジタルデータ補正エンコード回路 5 の出力データに係わる複数の下位ビット用基準電圧を選択し、その複数の下位ビット用基準電圧の信号を下位ビット用コンパレータ群回路 2 b の各下位ビット用コンパレータ回路 B の入力端子に接続する。

#### [0052]

各下位ビット用コンパレータ回路Bの他の入力端子には入力電圧VINを接続して、各下位ビット用コンパレータ回路Bに、入力電圧VINと与えられた基準電圧とを比較させる。

## [0053]

(下位ビットディジタルデータ作成回路の動作)

以下で、図2を参照して、第2の実施形態の下位ビットディジタルデータ作成回路の動作を説明する。

### [0054]

(下位ビット用基準電圧選択スイッチ群6の動作)

図2の回路図のように、下位ビット用基準電圧選択スイッチ群6が、上位ビットディジタルデータ補正エンコード回路5の出力信号により、すなわち、図1の高精度上位ビットディジタルデータ作成回路が作成した高精度上位ビットディジタルデータに制御される。そして、下位ビット用基準電圧選択スイッチ群6は、上位ビットディジタルデータ補正エンコード回路5の出力データに係わる複数の下位ビット用基準電圧を選択し、下位ビット用コンパレータ群回路2bの各下位ビット用コンパレータ回路Bに接続する。

[0055]

詳しくは、下位ビット用基準電圧選択スイッチ群 6 が、上位ビットディジタルデータ補正エンコード回路 5 の出力する高精度上位ビットディジタルデータにより制御されて下位ビット用基準電圧選択スイッチ 6 a を選択して複数の下位ビット用基準電圧を選択し、下位ビット用コンパレータ群回路 2 b の各下位ビット用コンパレータ回路 B に接続する。

[0056]

図2の様に、下位ビット用コンパレータ群回路2bの各下位ビット用コンパレータ回路Bの出力信号の2値データを下位ビット用エンコード回路5bに導く。下位ビット用エンコード回路5bは、各下位ビット用コンパレータ回路Bの出力信号を用いて、下位ビットである2ビットの下位ビットディジタルデータを作成する。

[0057]

こうして、上位ビットディジタルデータ補正エンコード回路 5 が出力した正確な上位ビットディジタルデータと、下位ビット用エンコード回路 5 b が出力した 2 ビットの下位ビットディジタルデータとを合わせて、正確に A D 変換したディジタルデータを得ることができる。

[0058]

< 第 3 の実施形態 >

以下本発明の第3の実施形態について図3を参照して説明する。本実施形態のAD変換回路の構成は第1の実施形態と同様に、図3の様に、ラダー抵抗1と高精度上位ビットディジタルデータ作成回路と、下位ビットディジタルデータ作成回路で構成する。

[0059]

(高精度上位ビットディジタルデータ作成回路)

第3の実施形態は、図3の様に、高精度上位ビットディジタルデータ作成回路の上位ビット用低精度コンパレータ群回路2の、ラダー抵抗1が発生した複数の基準電圧を入力する入力端子に、ソースフォロア回路等で構成するバッファ回路7を設置する。また、上位ビット用低精度コンパレータ群回路2の、入力電圧VINを入力する入力端子に、ソースフォロア回路等で構成するバッファ回路8を設置する。

[0060]

それ以外の回路は、第1の実施形態又は第2の実施形態と同様に、複数の、仮上位ビット電圧選択回路3と、1つの高精度コンパレータ回路4と、上位ビットディジタルデータ補正エンコード回路5、下位ビットディジタルデータ作成回路で構成する。

[0061]

先の実施形態では、入力電圧VINの信号線に、低精度コンパレータ回路Aの入力端子が複数接続されることにより入力容量が大きくなってしまう問題があった。第3の実施形態は、バッファ回路8を用いることで、入力電圧VINの信号線に接続する入力容量を小さくできる効果がある。

[0062]

通常の回路では、低精度コンパレータ回路Aの入力端子にバッファ回路7とバッファ回路8を挿入するとバッファ回路のオフセットにより、低精度コンパレータ回路Aの変換誤差を生じる。しかし、本実施形態では、高精度コンパレータ回路4と、上位ビットディジ

10

20

30

40

タルデータ補正エンコード回路 5 を用いることで、正確な上位ビットディジタルデータを得ることができるので、バッファ回路 7 とバッファ回路 8 によるオフセット誤差を 1 L S B 以下にすれば、変換誤差を生じさせずにバッファ回路を挿入することが可能である。

#### [0063]

このため、通常では変換誤差を生じるために挿入することができないバッファ回路7とバッファ回路8を低精度コンパレータ回路Aの入力端子に設置することが可能になる効果がある。そして、そのバッファ回路7とバッファ回路8を挿入することにより、入力電圧VINの信号線に接続する入力容量と、ラダー抵抗1が発生した基準電圧の信号線に接続する入力容量を大きく減らすことができる効果がある。それにより、低精度コンパレータ回路Aの動作を高速化できる効果がある。

【符号の説明】

[0064]

1、101・・・ラダー抵抗

2 ・・・上位ビット用低精度コンパレータ群回路

2 b ・・・下位ビット用コンパレータ群回路

3・・・仮上位ビット電圧選択回路

3 a・・・3 入力論理和回路

3 b ・・・仮上位ビット電圧信号出力スイッチ回路

4・・・高精度コンパレータ回路

5・・・上位ビットディジタルデータ補正エンコード回路

5 b ・・・下位ビット用エンコード回路

6 ・・・下位ビット用基準電圧選択スイッチ群

6 a・・・下位ビット用基準電圧選択スイッチ

7、8・・・バッファ回路

102・・・コンパレータ群回路

103・・・エンコード回路

A・・・(上位ビット用)低精度コンパレータ回路

B・・・(下位ビット用)コンパレータ回路

C1・・・高精度コンパレータ回路用コンデンサ

D・・・インバータ

OutPut・・・ディジタルデータ

REF・・・リファレンス電圧

SW1・・・高精度コンパレータ回路入力端子スイッチ

SW2・・・高精度コンパレータ回路のインバータDの入出力短絡用スイッチ

VIN···入力電圧

10

20