### (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2017-85480 (P2017-85480A)

(43) 公開日 平成29年5月18日(2017.5.18)

| (51) Int.Cl. |      |            | F I  |      |   | テーマコード (参考) |

|--------------|------|------------|------|------|---|-------------|

| H03F         | 1/42 | (2006.01)  | HO3F | 1/42 |   | 5 J 5 O O   |

| H03F         | 1/34 | (2006.01)  | HO3F | 1/34 |   |             |

| H03F         | 3/45 | (2006, 01) | H03F | 3/45 | В |             |

#### 審査譜求 未譜求 譜求項の数 4 〇1. (全 14 頁)

|                       |                                                          | 番笡請水     | 木請水                                       | 請水坝     | (0)数 4 | OL   | (至   | 14 貝) |  |  |

|-----------------------|----------------------------------------------------------|----------|-------------------------------------------|---------|--------|------|------|-------|--|--|

| (21) 出願番号<br>(22) 出願日 | 特願2015-214552 (P2015-214552)<br>平成27年10月30日 (2015.10.30) | (71) 出願人 | 000000572<br>アンリツ株式会社<br>神奈川県厚木市恩名五丁目1番1号 |         |        |      |      |       |  |  |

|                       |                                                          | (74)代理人  | 弁理士 早川 誠志                                 |         |        |      |      |       |  |  |

|                       |                                                          | (72) 発明者 |                                           |         |        |      |      |       |  |  |

|                       |                                                          |          |                                           |         |        |      |      | アン    |  |  |

|                       |                                                          |          |                                           |         |        |      |      |       |  |  |

|                       |                                                          | Fターム (参  | 考) 5J5                                    | 00 AA01 | AA12   | AC62 | AC63 | AF09  |  |  |

|                       |                                                          |          |                                           | AF17    | AH02   | AH25 | AH29 | AK02  |  |  |

|                       |                                                          |          |                                           | AK05    | AMO1   | AM13 | AT01 | AT03  |  |  |

|                       |                                                          |          |                                           | DN01    | DN22   | DN23 | DP02 | NH23  |  |  |

|                       |                                                          |          |                                           | NMO2    |        |      |      |       |  |  |

|                       |                                                          |          |                                           |         |        |      |      |       |  |  |

|                       |                                                          |          |                                           |         |        |      |      |       |  |  |

|                       |                                                          |          |                                           |         |        |      |      |       |  |  |

### (54) 【発明の名称】帰還増幅回路およびその周波数特性制御方法

### (57)【要約】

【課題】安定に広帯域特性や高い周波数域でのピーキング特性を得られるようにする。

【解決手段】入力信号 Vin(+)、Vin(-)を初段トランジスタ22、32のベースで受け、そのコレクタに接続された初段負荷抵抗回路23、33に現れる初段出力信号 V1、V1 を次段トランジスタ24、34のベースに与え、そのコレクタに接続された次段負荷抵抗回路25、35に現れる次段出力信号 Vout、Vout を帰還用トランジスタ26、36のベースに入力し、そのエミッタから初段負荷抵抗回路23、33を介して次段トランジスタ24、34のベースに帰還する帰還増幅回路において、次段出力信号 Vout、Vout の信号出力点と帰還用トランジスタ26、36のベースとの間が、所定周波数より高域の信号成分の帰還量を減少させるための帰還制御用の抵抗27、37を介して接続されている。

【選択図】図1

#### 【特許請求の範囲】

### 【請求項1】

入力信号を初段トランジスタ(22、32)のベースで受け、該初段トランジスタのコレクタに接続された初段負荷抵抗回路(23、33)に現れる初段出力信号を、次段トランジスタ(24、34)のベースに与え、該次段トランジスタのコレクタに接続された次段負荷抵抗回路(25、35)に現れる次段出力信号を、帰還用トランジスタ(26、36)のベースに入力し、該帰還用トランジスタのエミッタから前記初段負荷抵抗回路を介して前記次段トランジスタのベースに帰還する帰還増幅回路において、

前記次段負荷抵抗回路に現れる次段出力信号の信号出力点と、前記帰還用トランジスタのベースとの間が、前記次段トランジスタのベースに帰還される信号成分のうち、所定周波数より高域の信号成分の帰還量を減少させるための帰還制御用の抵抗(27、37)を介して接続されていることを特徴とする帰還増幅回路。

### 【請求項2】

前記帰還用トランジスタのベースに帰還制御用のキャパシタ(28、38)が接続され、該帰還制御用のキャパシタと前記帰還制御用の抵抗とで形成されたRC型のローパスフィルタにより、前記次段トランジスタのベースに帰還される信号成分のうち、所定周波数より高域の信号成分の帰還量を減少させることを特徴とする請求項1記載の帰還増幅回路

### 【請求項3】

入力信号を初段トランジスタ(22、32)のベースで受け、該初段トランジスタのコレクタに接続された初段負荷抵抗回路(23、33)に現れる初段出力信号を、次段トランジスタ(24、34)のベースに与え、該次段トランジスタのコレクタに接続された次段負荷抵抗回路(25、35)に現れる次段出力信号を、帰還用トランジスタ(26、36)のベースに入力し、該帰還用トランジスタのエミッタから前記初段負荷抵抗回路を介して前記次段トランジスタのベースに帰還する帰還増幅回路の周波数特性制御方法において、

前記次段負荷抵抗回路に現れる次段出力信号の信号出力点と、前記帰還用トランジスタのベースとの間を、帰還制御用の抵抗(27、37)を介して接続し、該帰還制御用の抵抗により、前記次段トランジスタのベースに帰還される信号成分のうち、所定周波数より高域の信号成分の帰還量を減少させて、帰還増幅回路の前記所定周波数より高域の利得を制御することを特徴とする帰還増幅回路の周波数特性制御方法。

### 【請求項4】

前記帰還用トランジスタのベースに帰還制御用のキャパシタ(28、38)を接続し、該帰還制御用のキャパシタと前記帰還制御用の抵抗とで形成されるRC型のローパスフィルタにより、前記次段トランジスタのベースに帰還される信号成分のうち、所定周波数より高域の信号成分の帰還量を減少させて、帰還増幅回路の前記所定周波数より高域の利得を制御することを特徴とする請求項3記載の帰還増幅回路の周波数特性制御方法。

### 【発明の詳細な説明】

### 【技術分野】

#### [0001]

本発明は、帰還増幅回路の周波数特性を安定に広帯域化あるいは高域の利得にピーキングを生じさせるための技術に関する。

#### 【背景技術】

### [0002]

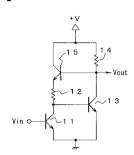

広帯域な信号増幅が可能な増幅回路として帰還増幅回路が知られている。帰還増幅回路は、図13に示すように、入力信号 Vinを初段トランジスタ11のベースで受け、その初段トランジスタ11のコレクタと初段負荷抵抗12(帰還抵抗)との接続点に現れる初段出力信号を、次段トランジスタ13のベースに与え、次段トランジスタ13のコレクタと次段負荷抵抗14との接続点に現れる次段出力信号(帰還増幅回路の出力信号) Voutを、帰還用トランジスタ15のエミッタから初段

10

20

30

30

40

(3)

負荷抵抗 1 2 を介して次段トランジスタ 1 3 のベースに逆位相で帰還する構成を有している。

[0003]

このように、帰還増幅回路は、2段接続されたエミッタ接地型増幅回路の出力信号をエミッタフォロア回路で初段負荷抵抗を介して次段トランジスタのベースに負帰還しているため、広帯域な動作が可能となる。

[0004]

なお、各種の通信装置や測定装置等に実装される増幅回路では、例えば特許文献 1 に示しているように、上記帰還増幅回路を 2 組用い、各組の初段トランジスタのエミッタ同士を共通の定電流源に接続し、各組の次段トランジスタのエミッタ同士を共通の定電流源に接続して差動動作させるものが一般的である。

[0005]

上記した従来の帰還増幅回路の電圧利得 A v は、初段トランジスタによる増幅部の裸利得を A v 1 (= g  $_{m-1}$  ・ R  $_{L-1}$ )、次段トランジスタによる増幅部の裸利得を A v 2 (= g  $_{m-2}$  ・ R  $_{L-2}$ )とし、帰還用トランジスタ 1 5 による次段出力信号 V out の帰還がゲイン 1 で十分広帯域に行なわれると仮定すると、特許文献 1 にも示されているように、

$A v = A v 1 \cdot A v 2 / K .....(1)$

K = (1 + g <sub>m 2</sub> ・ R <sub>L 2</sub> ) (1 + j a) (1 + j b) (1 + j c) ......(2) で表される。

[0006]

ここで、  $g_{m,1}$  は初段トランジスタの相互コンダクタンス、  $g_{m,2}$  は次段トランジスタの相互コンダクタンス、  $R_{L,1}$  は初段負荷抵抗の抵抗値、  $R_{L,2}$  は次段負荷抵抗の抵抗値、  $R_{L,2}$  は次段負荷抵抗の抵抗値、  $R_{L,2}$  は次段トランジスタのコレクタの負荷容量、  $R_{L,2}$  は次段トランジスタのベースでの時定数、  $R_{L,2}$  は次段トランジスタのベースでの時定数、  $R_{L,2}$  はかり、  $R_{L,2}$  は次段トランジスタのベースでの時定数、  $R_{L,2}$  はかり、  $R_{L,2}$  は次段トランジスタのベース抵抗を  $R_{L,2}$  は次段トランジスタのベース抵抗を  $R_{L,2}$  なり、  $R_{L,2}$  とすれば、  $R_{L,2}$  と  $R_{L,2}$  と

[0007]

$a = C_{1} \cdot r_{b1} \dots \dots (3)$   $b = \{C_{2} \cdot (R_{L1} + r_{b2}) / (1 + g_{m2} \cdot R_{L2})\}$   $\times \{(1 + j C_{L} \cdot R_{L2}) / (1 + j C_{)}\} \dots \dots (4)$   $c = C_{L} \cdot R_{L2} / (1 + g_{m2} \cdot R_{L2}) \dots \dots (5)$

[0008]

上式(1)(2)において、角周波数 が低く、 j a、 j b、 j c の各値が1に対して無視できる程度に小さい範囲では、 K は(1+gm2・R <sub>L 2</sub> )に近似され、利得A v は、

$A \lor = A \lor 1 \cdot A \lor 2 / (1 + g_{m2} \cdot R_{L2}) = A \lor 1 \cdot A \lor 2 / (1 + A \lor 2)$ で一定となり、仮に1  $A \lor 2$ であれば、帰還増幅回路全体の利得  $A \lor$ は、ほぼ初段の利得に  $A \lor 1$ に等しくなる。

[0009]

また、角周波数 が高くなって、 j a、 j b、 j c の各値が1に対して無視できない大きさになると、利得Avは、角周波数 が高くなるにつれて低下することになるが、帰還が掛かることで、次段トランジスタのベースおよびコレクタの時定数が、帰還が無い状態に比べて1/(1+g m 2 ・ R L 2 )に低減されるため、帰還が無い増幅回路に比べて広帯域な特性が得られる。

【先行技術文献】

【特許文献】

[0010]

【特許文献1】特開平2-223209号公報

【発明の概要】

50

10

20

30

#### 【発明が解決しようとする課題】

### [0011]

このように、帰還増幅回路は、帰還が無い増幅回路に比べて広帯域な特性が得られるが、近年の通信速度の高速化等に対応するために、さらなる広帯域化や高い周波数域での高利得化が望まれている。

### [0012]

これを実現する一つの技術として、前記した特許文献 1 では、次段負荷抵抗が接続されている帰還増幅回路の信号出力端子に、一端が接地された容量を接続することによりピーキング特性を得る技術が開示されている。

### [0013]

しかしながら、上記した従来回路では、次段負荷抵抗に直に接続された容量のみでピーキング特性を得るので、上記容量により次段トランジスタのコレクタの時定数が大きくなってしまい、高周波領域での利得の低下が急峻になり、得られる帯域が制限されるという問題があった。また、帰還増幅回路の信号出力端子に容量を直に接続するため、出力反射特性が悪化するという問題もあった。

#### [0014]

また、大きなピーキング量を得るためには、大面積の容量を形成する必要があり、回路 レイアウトにおいて各配線が長くなってしまい、余計な配線の寄生成分や帰還信号の位相 遅れが生じやすくなり、それにより意図しない共振や発振が発生して回路の動作が不安定 になる問題があった。

#### [0015]

また、従来回路では、次段負荷抵抗に接続された容量のみでピーキング特性を得るため 、ピーキング量とピーク周波数を自由に設定することができない不便さがあった。

#### [ 0 0 1 6 ]

本発明は、これらの問題を解決し、安定な動作を維持しながら広帯域化する、あるいは高い周波数域でピーキング特性を得ることができる帰還増幅回路およびその周波数特性制御方法を提供することを目的としている。

#### 【課題を解決するための手段】

### [0017]

前記目的を達成するために、本発明の請求項1の帰還増幅回路は、

入力信号を初段トランジスタ(22、32)のベースで受け、該初段トランジスタのコレクタに接続された初段負荷抵抗回路(23、33)に現れる初段出力信号を、次段トランジスタ(24、34)のベースに与え、該次段トランジスタのコレクタに接続された次段負荷抵抗回路(25、35)に現れる次段出力信号を、帰還用トランジスタ(26、36)のベースに入力し、該帰還用トランジスタのエミッタから前記初段負荷抵抗回路を介して前記次段トランジスタのベースに帰還する帰還増幅回路において、

前記次段負荷抵抗回路に現れる次段出力信号の信号出力点と、前記帰還用トランジスタのベースとの間が、前記次段トランジスタのベースに帰還される信号成分のうち、所定周波数より高域の信号成分の帰還量を減少させるための帰還制御用の抵抗(27、37)を介して接続されていることを特徴とする。

### [0018]

また、本発明の請求項2の帰還増幅回路は、請求項1記載の帰還増幅回路において、前記帰還用トランジスタのベースに帰還制御用のキャパシタ(28、38)が接続され、該帰還制御用のキャパシタと前記帰還制御用の抵抗とで形成されたRC型のローパスフィルタにより、前記次段トランジスタのベースに帰還される信号成分のうち、所定周波数より高域の信号成分の帰還量を減少させることを特徴とする。

#### [0019]

また、本発明の請求項3の帰還増幅回路の周波数特性制御方法は、

入力信号を初段トランジスタ(22、32)のベースで受け、該初段トランジスタのコレクタに接続された初段負荷抵抗回路(23、33)に現れる初段出力信号を、次段トラ

10

20

30

40

ンジスタ(24、34)のベースに与え、該次段トランジスタのコレクタに接続された次段負荷抵抗回路(25、35)に現れる次段出力信号を、帰還用トランジスタ(26、36)のベースに入力し、該帰還用トランジスタのエミッタから前記初段負荷抵抗回路を介して前記次段トランジスタのベースに帰還する帰還増幅回路の周波数特性制御方法において、

前記次段負荷抵抗回路に現れる次段出力信号の信号出力点と、前記帰還用トランジスタのベースとの間を、帰還制御用の抵抗(27、37)を介して接続し、該帰還制御用の抵抗により、前記次段トランジスタのベースに帰還される信号成分のうち、所定周波数より高域の信号成分の帰還量を減少させて、帰還増幅回路の前記所定周波数より高域の利得を制御することを特徴とする。

[0020]

また、本発明の請求項4の帰還増幅回路の周波数特性制御方法は、請求項3記載の帰還増幅回路の周波数特性制御方法において、

前記帰還用トランジスタのベースに帰還制御用のキャパシタ(28、38)を接続し、該帰還制御用のキャパシタと前記帰還制御用の抵抗とで形成されるRC型のローパスフィルタにより、前記次段トランジスタのベースに帰還される信号成分のうち、所定周波数より高域の信号成分の帰還量を減少させて、帰還増幅回路の前記所定周波数より高域の利得を制御することを特徴とする。

### 【発明の効果】

### [0021]

このように、本発明の請求項1、3では、帰還増幅回路の次段負荷抵抗回路に現れる次段出力信号の信号出力点と、帰還用トランジスタのベースとの間が、帰還制御用の抵抗を介して接続されている。

[0022]

このようにエミッタフォロア回路を形成する帰還用トランジスタのベースに帰還制御用の抵抗を直列に挿入したことで、エミッタフォロア回路の高周波領域で利得が低下する周波数が、帰還制御用の抵抗が無い場合に比べて低い方に変化する。

[0023]

これは、エミッタフォロア回路の周波数特性の極(カットオフ周波数)が、帰還制御用の抵抗の値が大きくなるほど低くなることに起因して生じる作用であり、この作用によって、帰還用トランジスタから次段トランジスタへの信号の帰還量が低下し始める周波数が、帰還制御用の抵抗が無い場合に比べて低くなり、その結果、その周波数より高域で帰還増幅回路全体の利得が上昇し、周波数特性を広帯域化したり、ピーキングを生じさせることができる。また、信号出力端子に容量を接続する従来方法に比べ、ピーク周波数以上での利得低下が小さく、出力反射特性の劣化も生じない。

[0024]

また、本発明の請求項 2 、 4 では、帰還用トランジスタのベースに帰還制御用のキャパシタを接続して帰還制御用の抵抗とで R C 型のローパスフィルタを形成している。このため、帰還用トランジスタのベースに入力される信号が減衰し始める周波数と減衰度合いが、 R C 型のローパスフィルタの特性により調整でき、帰還制御用の抵抗の抵抗値とキャパシタの容量値の組合せによって、ピーキング量およびピーク周波数を高い自由度で設定できる。

【図面の簡単な説明】

[0025]

【図1】本発明の実施形態の回路図

【 図 2 】 帰 還 制 御 用 の 抵 抗 お よ び コ ン デ ン サ の 有 無 に よ る 帰 還 量 の 周 波 数 特 性 の 変 化 を 示 す 図

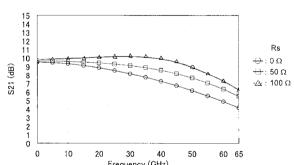

- 【図3】実施形態の帰還制御用の抵抗の抵抗値変化に対する周波数特性図

- 【図4】入力部に用いたエミッタフォロア回路

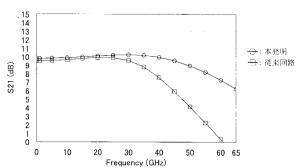

- 【図5】実施形態と従来回路の利得の周波数特性図

10

20

30

40

10

20

30

40

50

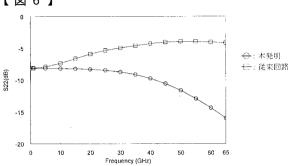

- 【図6】実施形態と従来回路の出力反射係数の周波数特性図

- 【図7】本発明の別の実施形態の回路図

- 【図8】本発明の別の実施形態の帰還制御用のキャパシタの容量変化に対する利得の周波数特性図

- 【図9】本発明の別の実施形態の帰還制御用のキャパシタの容量変化に対する出力反射係数の周波数特性図

- 【図 1 0 】本発明の別の実施形態の抵抗とキャパシタの組合せに対する利得の周波数特性図

- 【図11】非差動型(シングル型)の帰還増幅回路に本発明を適用した例を示す回路図

- 【図12】負荷抵抗回路を2つの抵抗の直列接続回路で形成した実施形態の回路図

- 【図13】従来回路を示す図

- 【発明を実施するための形態】

- [0026]

- 以下、図面に基づいて本発明の実施の形態を説明する。

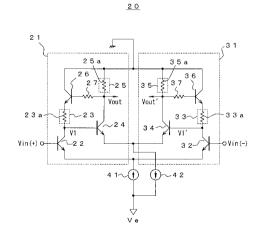

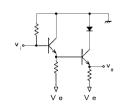

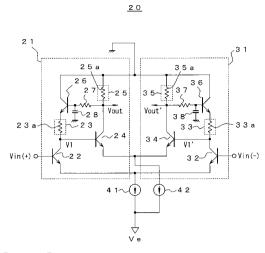

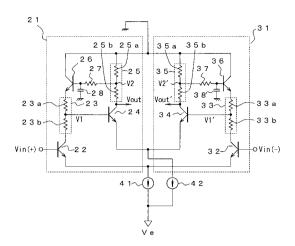

- 図1は、本発明を適用した帰還増幅回路20の構成を示す図である。

- [0027]

この帰還増幅回路 2 0 は、二組の帰還増幅回路 2 1、3 1を用いた差動型のものであり、一方の帰還増幅回路 2 1 は、入力信号 V in(+)を、初段トランジスタ 2 2 のベースで受け、初段トランジスタ 2 2 のコレクタに一端側が接続された初段負荷抵抗回路 2 3 (帰還抵抗回路)に現れる初段出力信号 V 1を、次段トランジスタ 2 4 のベースに与え(抵抗を介して入力する場合もある)、次段トランジスタ 2 4 のコレクタに一端側が接続された次段負荷抵抗回路 2 5 に現れる次段出力信号(帰還増幅回路 2 0 の一方の出力信号) Voutを、帰還用トランジスタ 2 6 のベースに与え、帰還用トランジスタ 2 6 のエミッタから初段負荷抵抗回路 2 3 を介して次段トランジスタ 2 4 のベースに逆位相で帰還する構成を有している。

[0028]

他方の帰還増幅回路31も同様に、入力信号 Vin(-)を、初段トランジスタ32のベースで受け、その初段トランジスタ32のコレクタに一端側が接続された初段負荷抵抗回路33(帰還抵抗回路)に現れる初段出力信号 V1 を、次段トランジスタ34のベースに与え、次段トランジスタ34のコレクタに一端側が接続された次段負荷抵抗回路35に現れる次段出力信号(帰還増幅回路20の他方の出力信号) Vout を、帰還用トランジスタ36のベースに与え、帰還用トランジスタ36のエミッタから初段負荷抵抗回路33を介して次段トランジスタ34のベースに逆位相で帰還する構成を有している。

[0029]

そして、二組の帰還増幅回路21、31が差動動作するように、帰還増幅回路21の初段トランジスタ22のエミッタと帰還増幅回路31の初段トランジスタ32のエミッタが共通の定電流源41を介して電源Veに接続され、帰還増幅回路21の次段トランジスタ24のエミッタと帰還増幅回路31の次段トランジスタ34のエミッタが、共通の定電流源42を介して電源Veに接続されている。また、帰還増幅回路21の次段負荷抵抗回路25と帰還用トランジスタ26のコレクタ、帰還増幅回路31の次段負荷抵抗回路35と帰還用トランジスタ36のコレクタはアース(電源Veより高電位の電源に接続する場合もある)に接続されている。

[0030]

なお、ここでは、初段負荷抵抗回路23、33がそれぞれ単一の抵抗23a、33aで形成され、その抵抗23a、33aと初段トランジスタ22、32のコレクタとの接続点に現れる初段出力信号V1、V1 を出力し、次段負荷抵抗回路25、35が単一の抵抗25a、35aと次段トランジスタ24、34のコレクタとの接続点に現れる次段出力信号Vout、Vout を出力する回路例について説明するが、後述するように、初段負荷抵抗回路23、33や次段負荷抵抗回路25、35をそれぞれ二つの抵抗の直列接続回路で形成し、その二つの抵抗の接続点から信号を出力さ

せる回路の場合でも本発明を適用できる。

### [0031]

これら帰還増幅回路 2 1、3 1の高域側の周波数特性を改善して広帯域化するために、帰還増幅回路 2 1の次段出力信号 Vout の信号出力点(この回路例では次段トランジスタ 2 4 のコレクタと次段負荷抵抗回路 2 5 との接続点)と帰還用トランジスタ 2 6 のベースの間が、所定抵抗値 R s の帰還制御用の抵抗 2 7 を介して接続され、帰還増幅回路 3 1 の次段出力信号 Vout の信号出力点(次段トランジスタ 3 4 のコレクタと次段負荷抵抗回路 3 5 との接続点)と、帰還用トランジスタ 3 6 のベースの間も所定抵抗値 R s の帰還制御用の抵抗 3 7 を介して接続されている。

### [0032]

次に、上記構成の帰還増幅回路20の基本的な動作について説明するが、二組の帰還増幅回路21、31の初段トランジスタ22、32の特性、初段負荷抵抗回路23、33の抵抗値、次段トランジスタ24、34の特性、次段負荷抵抗回路25、35の抵抗値、帰還用トランジスタ26、36の特性、帰還制御用の抵抗27、37の抵抗値は互いに等しいものとし、定電流源41、42により、各トランジスタの動作点が非飽和領域で適正に動作するように設定されているものとする。

### [0033]

ここで、二組の帰還増幅回路21、31に、振幅が等しく互いに位相が反転した入力信号 Vin(+)、 Vin(-)が与えられ、一方の入力信号 Vin(+)の電圧が上昇した場合、帰還増幅回路21の初段トランジスタ22に流れる電流が増大し、それに伴って初段出力信号 V1の電圧が減少し、次段トランジスタ24に流れる電流が減少し、次段出力信号 Vout の電圧が上昇する。

### [0034]

この次段出力信号 Vout は、帰還制御用の抵抗 2 7 を介して帰還用トランジスタ 2 6 のベースに入力されているので、次段出力信号 Vout の電圧が上昇すると帰還用トランジスタ 2 6 のエミッタ電圧も上昇するので、入力信号 Vin(+)の電圧上昇による初段トランジスタ 2 2 と初段負荷抵抗回路 2 3 との接続点の電圧降下が抑制されて負帰還が掛かることになる。また、入力信号 Vin(+)の電圧が下降する場合には、上記動作と反対の電流変化、電圧変化が起きるため、次段出力信号 Vout には、 2 段接続のエミッタ接地型増幅器が有する利得から負帰還量分を減じた利得で入力信号 Vin(+)を増幅した信号が現れることになる。

### [0035]

一方の帰還増幅回路 2 1 が上記動作をしている状態で、他方の帰還増幅回路 3 1 は、 Vin(+)に対して位相が反転した入力信号 Vin(-)が入力され、初段トランジスタ 3 2 の電流は、共通の定電流源 4 1 に接続されている帰還増幅回路 2 1 の初段トランジスタ 2 2 の電流の増減変化と逆に増減変化する。同様に、次段トランジスタ 3 4 の電流は、共通の定電流源 4 2 に接続されている帰還増幅回路 2 1 の次段トランジスタ 2 4 の電流の増減変化と逆に増減変化するので、次段出力信号 Vout に対して位相が反転した信号が現れることになる。

### [0036]

この帰還増幅回路20のように、エミッタフォロア回路を形成する帰還用トランジスタ26、36のベースに帰還制御用の抵抗27、37を直列に挿入したことで、エミッタフォロア回路の高周波領域で利得が低下する周波数が、帰還制御用の抵抗が無い場合に比べて低い方に変化する。これは、エミッタフォロア回路の周波数特性の極(またはカットオフ周波数)が、帰還制御用の抵抗の値が大きくなるほど低くなることに起因して生じる作用であり、この作用によって、帰還用トランジスタから次段トランジスタへの信号の帰還量が低下し始める周波数が、帰還制御用の抵抗が無い場合に比べて低くなり、その結果、その周波数より高域で帰還増幅回路全体の利得が上昇し、周波数特性を広帯域化することができる。

### [0037]

10

20

30

帰還用トランジスタ26、36が、通常のバイポーラトランジスタとすると、上記トランジスタで構成されるエミッタフォロア回路の極の周波数 p <sub>1</sub> は、近似的に下記の式となる。

$| p_1 | = 1 / (2 R_1 C)$

$R_1 = r \{ (R_S + r_b + R_E) / (1 + g_m R_E) \} \dots (6)$

ただし、r、r<sub>b</sub>、C、g<sub>m</sub>は、帰還用トランジスタのベース・エミッタ間抵抗、ベース抵抗、ベース・エミッタ間容量、相互コンダクタンスであり、R<sub>S</sub>は、帰還制御用抵抗の抵抗値、R<sub>E</sub>は、帰還用トランジスタのエミッタに接続された抵抗の抵抗値である。また、記号XYは、XとYの並列抵抗を示す。

#### [0038]

上式より、ベースに抵抗R<sub>S</sub>が接続されていない場合に比べて、ベースに抵抗R<sub>S</sub>が接続されている場合の方が、エミッタフォロア回路のカットオフ周波数が低くなる。

#### [0039]

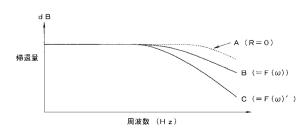

このように、エミッタフォロア回路のベースに抵抗を直列に接続することで、エミッタフォロア回路の周波数特性を、ベースに抵抗が接続されていない状態の図 2 の特性 A から特性 B のようにシフトさせることができる。

### [0040]

この特性 B は、帰還制御用の抵抗 2 7、 3 7 がベースに接続された帰還用トランジスタ 2 6、 3 6 で構成されるエミッタフォロア回路の特性を示すものであり、この特性 B を伝達関数 F ( ) ( F ( 0 ) 1 ) と仮定して、帰還増幅回路 2 0 全体の特性を求めると、

$Av = (g_{m1} \cdot R_{L1}) (g_{m2} \cdot R_{L2}) / K = Av 1 \cdot Av 2 / K ..... (7)$

$K = (1 + F () \cdot g_{m2} \cdot R_{L2})$  $\times (1 + j \quad a) (1 + j \quad b) (1 + j \quad c) \dots (8)$

## で表される。 【 0 0 4 1 】

前記同様に、 $g_{m-1}$  は初段トランジスタ22、32の相互コンダクタンス、 $g_{m-2}$  は次段トランジスタ24、34の相互コンダクタンス、 $R_{L-1}$  は初段負荷抵抗回路23、33の抵抗値、 $R_{L-2}$  は次段負荷抵抗回路25、35の抵抗値、 $C_{L}$  は次段トランジスタ24、34のコレクタの負荷容量、a は初段トランジスタ22、32のベースでの時定数、b は次段トランジスタ24、34のベースでの時定数、 c は次段トランジスタ24、34のコレクタでの時定数である。

#### [0042]

初段トランジスタ22、32の内部のベース抵抗を $r_{b-1}$ 、入力容量を $C_{1}$ 、次段トランジスタ24、34の内部のベース抵抗を $r_{b-2}$ 、入力容量を $C_{2}$ とすれば、a、b 、 c はそれぞれ次のように表される。

### [0043]

$a = C_{1} \cdot r_{b1} \dots (9)$   $b = \{C_{2} \cdot (R_{L1} + r_{b2}) / (1 + F() \cdot g_{m2} \cdot R_{L2}) \}$   $\times \{ (1 + j C_{L} \cdot R_{L2}) / (1 + j C_{)} \} \dots (10)$   $c = C_{L} \cdot R_{L2} / (1 + F() \cdot g_{m2} \cdot R_{L2}) \dots (11)$

#### [0044]

式(7)、(8)において、角周波数 が低く、 j a、 j b 、 j c の各値が 1 に対して無視できる程度に小さく、 F ( ) が 1 に近い範囲では、 K は(1 + g  $_{m 2}$  ・ R  $_{1 2}$ )に近似され、電圧利得 A  $_{2}$  は、

$A v = A v 1 \cdot A v 2 / (1 + g_{m2} \cdot R_{L2})$ となり、帰還制御用の抵抗が無い場合と同じになる。

### [0045]

また、角周波数 が高くなり、 F ( ) が低下する周波数領域では、利得の分母の( 1 + F ( ) ・  $g_{m-2}$  ・  $R_{L-2}$  ) の項が低下(帰還量が低下)するので、利得  $A \lor$  が増加し

10

20

30

40

50

、周波数特性をより広帯域にすることができる。

#### [0046]

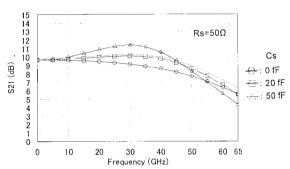

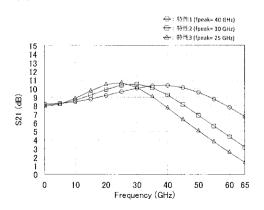

図3は、帰還増幅回路20において、帰還制御用の抵抗27、37の抵抗値R<sub>S</sub>を0、50、100に変えたときの利得(S21)の周波数特性を示している(実施例1)。ただし、同図は図4のエミッタフォロアからなる入力バッファ回路を帰還増幅回路20の前段(Vin(+)、Vin(-)端子)に接続して、上記入力バッファ回路のV<sub>i</sub>端子に信号入力した場合の特性である。また、回路を形成する各トランジスタは、ベース抵抗:十数、ベース・エミッタ間容量:十数fF(フェムトファラッド)、電流増幅率:約50、遮断周波数:約200GHzの標準的なInP(インジウム・リン)HBT(ヘテロバイポーラトランジスタ)である。

[0047]

図3から明らかなように、帰還制御用の抵抗の値R<sub>S</sub>が増すと、帰還増幅回路の帯域が向上することが判る。

### [0048]

また、図3において帰還制御用の抵抗を100 とした場合、30GHzで低域の利得に対する利得偏差が+0.4dB程度のピーキング特性が得られ、最も広帯域な特性となっている。従来回路を用いて同じように低域の利得に対する利得偏差が+0.4dB程度のピーキング特性を得るには、次段負荷抵抗に接続する容量値は230fF程度が必要となる。

### [0049]

そこで、230fFの容量を次段負荷抵抗回路に接続した場合の従来回路の利得と出力反射係数(S22)の周波数特性を図5、図6に示す。また、比較として帰還制御用の抵抗100 の場合の本発明の実施例回路の利得と出力反射係数の周波数特性も同グラフにそれぞれ示す。

### [0050]

図5より、従来回路では、25GHzで低域の利得に対する利得偏差が+0.4dB程度のピーキング特性が得られているが、25GHz以上での利得の低下が急峻であり、3dB帯域は本発明の実施例回路が62GHz程度であるのに対し、従来回路では43GHz程度と低くなっている。これは、従来回路では次段負荷抵抗回路(次段トランジスタのコレクタ)に直に容量を接続するので、次段トランジスタのコレクタの時定数が大きくなり、25GHz以上で帰還増幅回路全体の利得を低下させるためである。

### [0051]

また、図 6 より、本発明の実施例回路は低域での出力反射係数が - 8 d B 程度で周波数が高くなるほど低下しているのに対し、従来回路では帰還増幅回路の信号出力端子(Vout端子)に直に容量を接続するため、高周波領域で出力インピーダンスが低下し、 5 0 G H z において - 4 d B 程度まで悪化している。

### [0052]

また、従来回路では230fFの容量を回路上に形成する必要があるが、一般的な高周波 I C プロセスで用いられる窒化シリコン膜を誘電体として平行平板型のキャパシタを形成する方法では、230fFの容量値を得るには数百μm²もの面積を要する。それにより従来回路では回路が大型化し、各配線長が長くなり、意図しない共振や発振が生じやすくなる。一方、本発明の実施例回路では広帯域特性を得るため100 の抵抗を用いているが、一般的な高周波 I C プロセスで用いられる窒化タングステンシリサイド膜で抵抗体を形成する方法では、100 の抵抗値は従来回路の上記容量に比べ、1/10以下の面積で実現できる。そのため本発明の実施例回路では各配線を短くでき、帰還増幅回路の動作を不安定にすることなく広帯域化することができる。

#### [0053]

なお、本実施例では高周波ICプロセスで帰還増幅回路を形成する場合の帰還制御用の抵抗として、窒化タングステンシリサイド膜で形成する抵抗を一例として述べたが、別の材料やトランジスタのコレクタコンタクト層を用いて抵抗を形成してもよい。また、電界

10

20

30

40

効果トランジスタ等による可変抵抗素子を用いて、帰還制御用の抵抗の値を外部電圧で可変できる構成としてもよい。

### [0054]

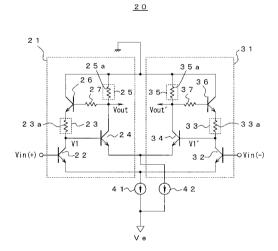

上記実施形態では、帰還用トランジスタ26、36のベースに帰還制御用の抵抗27、37を直列に挿入して、帰還量が低下しはじめる周波数を下げ、その周波数より高い領域で帰還増幅回路全体の利得を高くして広帯域化していたが、図7に示すように、帰還制御用の抵抗27、37と帰還用トランジスタ26、36のベースとの接続点に帰還制御用のキャパシタ28、38を接続することでRC型のローパスフィルタを形成し、高域側の帰還量をより高い自由度で制御することもできる。

### [0055]

このように構成した帰還増幅回路20では、帰還用トランジスタ26、36のベースにRC型のローパスフィルタが接続されたことになり、そのRC型のローパスフィルタの抵抗値およびキャパシタの容量値を選ぶことで、帰還用トランジスタで構成されるエミッタフォロア回路の周波数特性を、図2の特性A、Bに比べてカットオフ周波数が低い特性Cにできる。

#### [0056]

この特性 C を伝達関数 F ( ) とすれば、帰還増幅回路の利得 A v は、前記した式(7)、(8)の F ( ) を F ( ) に置き換え、さらに式(10)、(11)の次段負荷抵抗回路の時定数 R  $_{\rm L}$  2 C  $_{\rm L}$  を、帰還制御用の抵抗の抵抗値 R  $_{\rm S}$  と帰還制御用のキャパシタの容量値 C  $_{\rm S}$  の成分を考慮した式、

$R_{L_2}$  [  $C_L + C_S$  / (  $1 + R_S C_S j$  ) ] に置き換えた特性となる。

## [0057]

なお、帰還用トランジスタのベース・エミッタ間抵抗が、式(6)の $r_b$ 、 $R_s$ より十分高い場合、F() の極の周波数は、 $1/{2}$  ( $R_1C$  +  $R_sC_s$ )}と近似できる。

#### [0058]

したがって、帰還制御用キャパシタにより、帰還量が低下しはじめる周波数が低下し、その周波数より高域で帰還増幅回路全体の利得が上昇することになり、より広帯域な特性やピーキング特性が得られる。

### [0059]

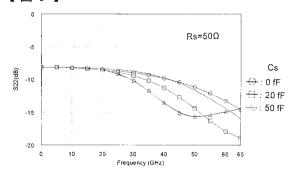

図 8 、図 9 は、実施例 1 と同じ条件のもとで、帰還制御用の抵抗 2 7 、 3 7 の値 R  $_S$  = 5 0 とし、帰還制御用のキャパシタ 2 8 、 3 8 の容量値 C  $_S$  を、 0 、 2 0 f F 、 5 0 f F としたときの利得(S 2 1 )と出力反射係数(S 2 2 )の周波数特性を示している。また、比較のために、実施例 1 の R  $_S$  = 1 0 0 のときの特性を同図に破線で示す。

### [0060]

図8から明らかなように、キャパシタ28、38の容量値 $C_s$ が増すと高域側の利得のピーキング量が増加している。これは $C_s$ を増すことにより帰還用トランジスタから次段トランジスタへの高域側の信号の帰還量が低下するためである。 $C_s$ =50fFでは、40GHzまでの利得はそれ以下の容量値の場合より大きいが、30GHz以上で利得の減衰が急峻になっている。これは帰還制御用キャパシタにより次段トランジスタのコレクタ時定数が大きくなる効果によるものである。 $C_s$ =20fFの場合、広帯域でかつ比較的平坦な周波数特性が得られており、帰還制御用のキャパシタを設けることで $R_s$ =50の抵抗値でも、実施例1の $R_s$ =100 の時と同程度の特性が得られている。また、 $C_s$ =20fFの場合、帰還制御用のキャパシタは帰還制御用の抵抗と同程度の面積で形成できるため、この構成でも回路面積を小さくできる。

### [0061]

また、図9より、出力反射係数は、Csがいずれの値の場合でも・8 d B 以下が得られている。これは、本発明の実施例回路の構成では、帰還制御用のキャパシタが帰還増幅回路の信号出力端子に対して帰還制御用の抵抗を介して接続され、帰還制御用の抵抗がない

10

20

30

40

場合に比べて信号出力端子に付加される容量成分の影響が軽減されるためである。

### [0062]

以上のように、抵抗値R<sub>S</sub>と容量値C<sub>S</sub>を最適化することにより、帰還増幅回路の高域側の帰還量を制御でき、安定に周波数特性を広帯域にしたり、所望の周波数でピーキング特性を得ることができる。

### [0063]

また、例えば通信システムで使用されるタイミング再生回路により抽出されたクロック信号を増幅する増幅器等では、特定の高い周波数の利得を大きくすることが要求される。図10は、本発明の帰還増幅回路において、抵抗値R<sub>S</sub>と容量値C<sub>S</sub>のみを調整して、低域に対するゲイン偏差+2dB程度のピーキングを生じさせ、さらにそのピーク周波数を調整した場合の特性である。それぞれピーク周波数が25GHz、30GHz、40GHz程度となっている。このように実施形態の回路では抵抗値R<sub>S</sub>と容量値C<sub>S</sub>を調整することで、所望の周波数でピーキングを生じさせ、特定の周波数で高いゲインを得られる。

### [0064]

なお、帰還制御用のキャパシタはIC表面に形成する平行平板型のキャパシタを一例として述べたが、半導体のpn接合部の容量を利用してもよく、その場合、バラクタダイオード等の可変容量素子を用いて、帰還制御用のキャパシタの容量値を外部電圧で調整できる構成としてもよい。

### [0065]

なお、上記実施例では、主材料としてInPで形成されたトランジスタで構成された帰還増幅回路について述べたが、シリコンやガリウム砒素等、別の材料で形成されたトランジスタで構成された帰還増幅回路についても本発明を同様に適用できる。

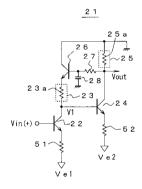

#### [0066]

上記実施形態は、二組の帰還増幅回路21、31を用いて差動型に構成したものであるが、帰還増幅回路21、31の一方だけを用いたシングル型の増幅回路の場合にも、本発明を適用できる。その場合には、例えば図11のように、初段トランジスタ22と次段トランジスタ24のエミッタにそれぞれ抵抗51、52を接続する構成としてもよい。この帰還増幅回路21では、帰還制御用の抵抗27とキャパシタ28を設けているが、キャパシタ28を省いて帰還制御用の抵抗27のみで、帰還量の制御を行なってもよい。

### [0067]

また、前記実施形態では、初段トランジスタと次段トランジスタとで増幅部を形成していたが、前記したように、図4に示したようなエミッタフォロアからなる入力バッファ回路を併用した帰還増幅回路についても本発明を同様に適用できる。

### [0068]

また、前記実施形態では、初段負荷抵抗回路23、33を単一の抵抗23a、33aで形成し、その抵抗23a、33aと初段トランジスタ22、32のコレクタとの接続点に現れる初段出力信号V1、V1 を出力し、次段負荷抵抗回路25、35を単一の抵抗25a、35aで形成し、その抵抗25a、35aと次段トランジスタ24、34のコレクタとの接続点に現れる次段出力信号Vout、Vout を出力していたが、図12に示すように、初段負荷抵抗回路23、33あるいは次段負荷抵抗回路25、35をそれぞれ2つの抵抗の直列接続回路で形成した回路にも本発明を適用できる。

#### [0069]

初段負荷抵抗回路を2つの抵抗の直列接続回路とする場合、一方の初段トランジスタ22のコレクタに接続された初段負荷抵抗回路23を形成する二つの抵抗23a、23bの接続点に現れる初段出力信号V1を次段トランジスタ24のベースに入力させ、他方の初段トランジスタ32のコレクタに接続された初段負荷抵抗回路33を形成する二つの抵抗33a、33bの接続点に現れる初段出力信号V1 を次段トランジスタ34のベースに入力させる。

### [0070]

また、次段負荷抵抗回路を2つの抵抗の直列接続回路とする場合、一方の次段トランジ

10

20

30

40

スタ24のコレクタに接続された次段負荷抵抗回路25を形成する二つの抵抗25a、25bの接続点を帰還用の信号出力点とし、この信号出力点と帰還用トランジスタ26のベースの間に帰還用の抵抗27を挿入して、次段出力信号V2を帰還させ、他方の次段トランジスタ34のコレクタに接続された次段負荷抵抗回路35を形成する二つの抵抗35a、35bの接続点を帰還用の信号出力点とし、この信号出力点と帰還用トランジスタ36のベースの間に帰還用の抵抗37を挿入して、次段出力信号V2 を帰還させる。なお、この回路の場合、帰還増幅回路としての出力信号Vout、Vout を、次段トランジスタ24、34のコレクタから出力させている。

### [0071]

上記図12の回路では、帰還制御用のキャパシタを用いていたが、帰還制御用の抵抗だけで構成することもできる。

#### 【符号の説明】

### [0072]

20……帰還増幅回路、21、31……帰還増幅回路、22、32……初段トランジスタ、23、33……初段負荷抵抗回路、24、34……次段トランジスタ、25、25、35、35、35 ……次段負荷抵抗回路、26、36……帰還用トランジスタ、27、37……帰還制御用の抵抗、28、38……帰還制御用のキャパシタ、41、42……定電流源

### 【図1】

### 【図2】

### 【図3】

【図4】

## 【図5】

## 【図6】

## 【図7】

## 【図8】

## 【図9】

# 【図11】

### 【図10】

# 【図12】

20

# 【図13】