# (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2015-225932 (P2015-225932A)

(43) 公開日 平成27年12月14日 (2015.12.14)

| (51) Int.Cl. |         |           | F I     |       |              | テーマコート   | ぶ (参考) |

|--------------|---------|-----------|---------|-------|--------------|----------|--------|

| HO1L         | 21/822  | (2006.01) | HO1L    | 27/04 | $\mathbf{F}$ | 5F038    |        |

| HO1L         | 27/04   | (2006.01) | HO1L    | 27/04 | T            | 5F083    |        |

| HO1L         | 21/8242 | (2006.01) | HO1L    | 27/10 | 681F         | 5J056    |        |

| HO1L         | 27/108  | (2006.01) | G11C    | 11/34 | 354F         | 5MO24    |        |

| G11C         | 11/4074 | (2006.01) | нозк    | 19/00 | 1 O 1 B      |          |        |

|              |         |           | 審査請求 未請 | 求 請求  | 項の数 10 OL    | (全 14 頁) | 最終頁に続く |

(21) 出願番号 (22) 出願日 特願2014-109364 (P2014-109364) 平成26年5月27日 (2014.5.27) (71) 出願人 595168543

マイクロン テクノロジー, インク. アメリカ合衆国, アイダホ州 83716 -9632, ボイズ, サウス フェデ ラル ウェイ 8000

(74)代理人 100080816

弁理士 加藤 朝道

(74)代理人 100098648

弁理士 内田 潔人

(74)代理人 100119415

弁理士 青木 充

(72) 発明者 赤松 宏

東京都中央区八重洲2-2-1 マイクロ

ンメモリジャパン株式会社内

最終頁に続く

# (54) 【発明の名称】半導体装置

# (57)【要約】

【課題】信号をある電源電位から第1の電源電位にレベル変換するにあたり第1の電源の低電圧化に対しても十分な動作マージを確保することができる装置の提供。

【解決手段】第1の節点と第2の節点との間に接続され、第1種別の厚さのゲート絶縁膜を有する第1のトランジスタと、第1の電位を与える第1の電源端子と、信号を出力する出力端子との間に接続され、前記第2の節点にゲートが接続され、第2種別の厚さのゲート絶縁膜を有する2のトランジスタと、前記出力端子と、第2の電位を与える第2の電源端子との間に接続され、ゲートが前記第1の節点に接続された、前記第1種別の厚さのゲート絶縁膜を有する第3のトランジスタと、を少なくとも含む回路を備える。

【選択図】図1

# 【特許請求の範囲】

### 【請求項1】

第1の節点と第2の節点との間に接続され、第1種別の厚さのゲート絶縁膜を有する第 1のトランジスタと、

第1の電位を与える第1の電源端子と、信号を出力する出力端子との間に接続され、前記第2の節点にゲートが接続され、第2種別の厚さのゲート絶縁膜を有する第2のトランジスタと、

前記出力端子と、第2の電位を与える第2の電源端子との間に接続され、ゲートが前記第1の節点に接続された、前記第1種別の厚さのゲート絶縁膜を有する第3のトランジスタと、

を少なくとも含む回路を備えたことを特徴とする半導体装置。

# 【請求項2】

前記回路は、前記第1の電源端子と前記第2の節点との間に接続され、ゲートが前記出力端子に接続され、前記第2種別の厚さのゲート絶縁膜を有する第4のトランジスタをさらに備える、ことを特徴とする請求項1記載の半導体装置。

#### 【請求項3】

前記第1のトランジスタのゲートは、前記第1の電源端子に接続されている、ことを特徴とする請求項1又は2記載の半導体装置。

# 【請求項4】

前記回路は、第3の電位を与える第3の電源端子と前記第1の節点との間に接続され、前記第1種別の厚さのゲート絶縁膜を有する第5のトランジスタと、

前記第1の節点と前記第2の電源端子との間に接続され、前記第1種別の厚さのゲート 絶縁膜を有する第6のトランジスタと、

をさらに備え、

前記第5及び第6のトランジスタのゲート同士は接続され、信号を入力する入力端子に接続されている、ことを特徴とする請求項1乃至3のいずれか1項に記載の半導体装置。

# 【請求項5】

前記第2の電位は接地電位であり、

前記第1、第3の電位はともに前記第2の電位よりも高い電位であり、前記第1の電位は、前記第3の電位よりも低電圧とされ、

前記回路は、前記入力端子から入力された、前記第3の電位と前記第2の電位で規定される振幅の信号を、前記第1の電位と前記第2の電位で規定される振幅の信号にレベル変換して前記出力端子から出力する、ことを特徴とする請求項4記載の半導体装置。

# 【請求項6】

前記第1種別の厚さのゲート絶縁膜は厚膜ゲート絶縁膜であり、

前記第2種別の厚さのゲート絶縁膜は薄膜ゲート絶縁膜である、ことを特徴とする請求 項1乃至5のいずれか1項に記載の半導体装置。

# 【請求項7】

前記第1及び第3のトランジスタが第1導電型であり、

前記第2のトランジスタが第2導電型であり、

少なくとも前記第2のトランジスタは、低電圧化された閾値を有する、ことを特徴とする請求項1乃至6のいずれか1項に記載の半導体装置。

# 【請求項8】

前記第4のトランジスタが第2導電型である、ことを特徴とする請求項2記載の半導体装置。

#### 【請求項9】

前記第5のトランジスタが第2導電型であり、

前記第6のトランジスタが第1導電型である、ことを特徴とする請求項4記載の半導体装置。

# 【請求項10】

10

20

30

40

前記回路を備えた半導体記憶装置を含む、請求項1乃至9のいずれか1項に記載の半導体装置。

【発明の詳細な説明】

#### 【技術分野】

#### [0001]

本発明は、半導体装置に関し、特にレベル変換に好適な半導体装置に関する。

#### 【背景技術】

# [00002]

DRAM(Dynamic Random Access Memory)等の半導体装置において、低消費電力化のために電源電圧は低電圧化の傾向にある。例えばDDR SDRAM(Double Data Rate Synchronous DRAM)の低電圧化・低消費電力化の規格を定めたLPDDR(Low Power DDR)についてみると、駆動電源電圧(VDD2)は、例えばモバイル向けのSDRAMに対応するLPDDR3では1.2Vであるが、次世代のモバイル向けのLPDDR4では1.1Vとされている。そして、この駆動電圧の低電圧化の傾向は、今後も続くものと思料される。一方、メモリセルアレイの駆動電圧(VDD1)は1.8Vとされている。メモリセルアレイの駆動電圧(VDD1)は1.8Vとされている。メモリセルアレイの駆動電圧(VDD1)は、セルアレイの微細化に伴うアレイの動作マージンの低下を補償するために、今後も低電圧化されないものと思料される。

#### [0003]

電源電圧VDD2の低電圧化の傾向により、メモリセルアレイの電源電圧VDD1の振幅の信号を駆動電圧VDD2の振幅にレベル変換するレベル変換回路の動作マージンが低下する傾向にある。例えば、レベル変換回路において、低電圧化した電源電圧VDD2の下限側のマージンが無くなり、電源変動等やトランジスタの閾値電圧のばらつき等により、動作不能あるいは動作不良等となる可能性が生じる。

#### [0004]

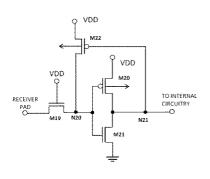

特許文献1には、図5に示すような構成の高耐圧型CMOS(Complementary Metal Oxide Semiconductor)受信回路が開示されている。図5は、特許文献1のFig.3に基づく図である。図5を参照すると、NFET (Nch Field Effect Transistor) M19のゲートはチップ電源VDDに接続されている。このため、NFET M19のドレインノードN20は最大VDD・Vth(VthはNFET M19の閾値電圧)とされ、受信回路(receiver)のパッド(PAD)に高電圧が印加された場合に、NFET M19は、内部回路(internal circuitry)を過電圧から保護するシールドデバイスとして機能する。PFET M22は、ノードN20をVDD・VthからVDDにブーストするプルアップトランジスタとして機能する。すなわち、パッド(PAD)がハイ(High)レベルのとき、ノードN21はロー(Low)レベルとなり、PFET M22が導通し、ノードN20をチップ電源VDD側にプルアップする。

#### [0005]

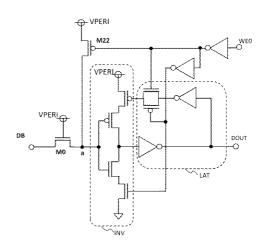

また、特許文献2には、図6に示すような、信号受信回路が開示されている。図6は、特許文献2の図5の一部の構成を示す図である。図6を参照すると、データバスDBと信号受信回路の入力端(ノード)aとの間に挿入され、データバスが電源電圧・NMOと、ランジスタの閾値電圧Vthに達すると非導通となるスイッチトランジスタM0と、信号受信回路の入力端aを電源VPERIに駆動するアシストトランジスタM22と、を備え、スイッチトランジスタM0及びアシストトランジスタM22によって信号受信回路のことなく、転送される信号の振幅を低減するのとを可能としている。制御信号WE0がHighレベルのとき、アシストトランジスタM22が導通し、ノードaを電源電圧VPERIに駆動し、インバータINVが活性化され、ラッチLATが活性化され、制御信号WE0がLowレベルのとき、アシストトランジスタM22は非導通となり、インバータINVが非活性化され、ラッチLATが活性化される。ラッチLATは、制御信号WE0がLowレベルとなる直前のインバータINVの出力をラッチする。

# [0006]

10

20

30

20

30

40

50

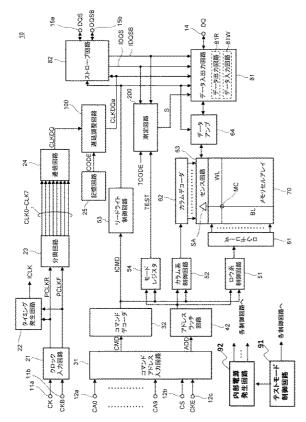

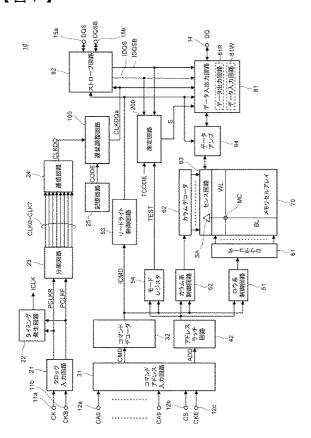

次に、本発明が適用される半導体装置の関連技術について特許文献3の開示に基づき、 その概略を説明する。図7は、特許文献3の図1の記載に対応する図である。図7を参照 すると、この半導体装置(SDRAM)10において、クロック入力回路21は、相補の 外部クロックCK、CKBを入力し内部クロック信号PCLKR、PCLKFを生成する 。タイミング発生回路22は、内部クロック信号PCLKR、PCLKFを入力し内部ク ロックICLKを生成する。分周回路23は、内部クロック信号PCLKR、PCLKF を入力し例えば8相の分周クロック信号CLK0~CLK7を生成する。逓倍回路24は 、8相の分周クロック信号CLK0~CLK7を逓倍し外部クロック信号CKの周波数と 同一の内部クロック信号CLKDQを生成する。遅延調整回路100は、記憶回路25の 情報CODEに基づきCLKDQの遅延を調整する。コマンドアドレス入力回路31は、 端子12a(コマンド・アドレス端子CA0~CA9)、12b(チップセレクト端子C S)、12c(クロックイネーブル端子CKE)の信号を入力する。コマンドデコーダ3 2は、コマンドアドレス入力回路31で入力したコマンドCMDをデコードする。アドレ スラッチ回路42はコマンドアドレス入力回路31で入力したアドレスADDをラッチす る。モードレジスタ54は、コマンドデコーダ32とアドレスラッチ回路42の出力を受 け、各種モードや設定パラメータを記憶する。

# [0007]

口ウ系制御回路51とカラム系制御回路52は、コマンドデコーダ32、アドレスラッ チ回路42の出力(ロウアドレス、カラムアドレス)を受ける。ロウデコーダ61は、ロ ウ系制御回路 5 1からのロウアドレスをデコードしメモリセルアレイ 7 0のワード線WL を選択する。カラムデコーダ62は、カラム系制御回路52からのカラムアドレスをデコ ードしセンス回路63に含まれるいずれかのセンスアンプSAを選択する。メモリセルア レイ70は、複数のワード線WLと複数のビット線BLを備え、ワード線WLとビット線 B L の交点にメモリセル M C を備えている。データアンプ 6 4 は、センス回路 6 3 によっ て増幅されたリードデータをさらに増幅し、これをデータ入出力回路81に供給し、ライ ト動作時においては、データ入出力回路81から供給されるライトデータを増幅する。デ - 夕入出力回路 8 1、 D Q 端子 1 4 からのデータを入力するデータ入力回路 8 1 W、 D Q 端子14にデータを出力するデータ出力回路81Rを備える。リードライト制御回路53 は、データアンプ64及びデータ入出力回路81の動作を制御する。ストローブ回路82 は、リード動作時には、リードデータDQに同期して外部データストローブ信号DQS、 DQSBの出力を行い、ライト動作時には、外部データストローブ信号DQS、DQSB に基づいて内部データストロープ信号IDQS、IDQSBの生成を行う。測定回路20 0は、モードレジスタ54からのTESTの活性化時に、クロック端子11a、11bに 外部クロック信号CK、CKBが入力された後、内部クロック信号CLKDQaの対応す るアクティブエッジがデータ入出力回路81に到達するまでの伝搬時間をモニタする。

# 【先行技術文献】

#### 【特許文献】

[0008]

【特許文献1】米国特許第5646809号明細書

【特許文献2】特開2011-091708号公報

【特許文献 3 】特開 2 0 1 3 - 1 3 1 2 7 7 号公報

【発明の概要】

【発明が解決しようとする課題】

[0009]

以下にレベルシフト回路の関連技術の問題点を分析する。

#### [0010]

CMOSインバータ等を含むレベル変換回路において、耐圧保護のため、ゲート絶縁膜の膜厚を厚くした膜厚トランジスタが用いられる。また電源VDD2の低電圧化に対応させて低閾値電圧としている。なお、VDD1系のCMOSインバータとVDD2系のCMOSインバータを2段カスケード接続し、CMOSインバータを厚膜トランジスタで構成

した構成の一例は、比較例として図4を参照して後に説明される。

# [0011]

MOSトランジスタのゲート酸化膜が厚くなると、その閾値電圧を下げることが難しくなることが知られている。電源VDD2の低電圧化に伴い、VDD2系の厚膜PMOSトランジスタのゲートに印加されるLow電位と電源電位VDD2との差が小さくなる傾向にあり、その差が厚膜PMOSトランジスタの閾値電圧の絶対値以下の場合、レベル変換回路自体が動作しなくなる。すなわち、低電位側の動作マージンの確保が困難となり、例えば、電源変動や、厚膜PMOSトランジスタの閾値のわずかなばらつき等によって、レベル変換回路の動作不能あるいは動作不良となる。

# [0012]

なお、特許文献1、2等に記載の発明は、パッド(PAD)への高電圧印加時に内部回路を保護するための構成(M19、M0)を備えたものであり、VDD2系のCMOSインバータにHighレベルが印加される時に有効に作用する発明であるが、Lowレベル印加時の問題点(低電圧化に伴うレベル変換回路の動作マージンの低下等により動作不能となる等)の解決に向けられた発明ではない。

# 【課題を解決するための手段】

# [0013]

本発明の一つの側面(aspect)によれば、第1の節点と第2の節点との間に接続され、第1種別の厚さのゲート絶縁膜を有する第1のトランジスタと、第1の電位を与える第1の電源端子と、信号を出力する出力端子との間に接続され、前記第2の節点にゲートが接続され、第2種別の厚さのゲート絶縁膜を有する第2のトランジスタと、前記出力端子と、第2の電位を与える第2の電源端子との間に接続され、ゲートが前記第1の節点に接続された、前記第1種別の厚さのゲート絶縁膜を有する第3のトランジスタと、を少なくとも含む回路を備えた半導体装置が提供される。

# 【発明の効果】

# [0014]

本発明によれば、信号をある電源電位から第1の電源電位にレベル変換するにあたり第 1 の電源の低電圧化に対しても十分な動作マージを確保することができる。

# 【図面の簡単な説明】

# [0015]

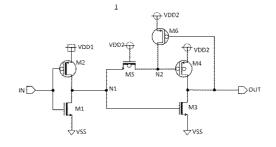

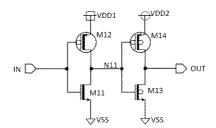

- 【図1】本発明の一実施形態のレベル変換回路の構成を例示する図である。

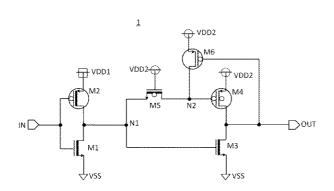

- 【図2】図1と、比較例(図4)のレベル変換回路の動作波形を例示する図である。

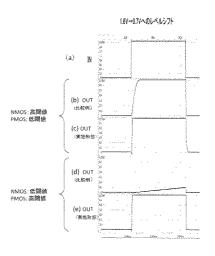

- 【図3】本発明の一実施形態の半導体装置の構成を例示する図である。

- 【図4】比較例のレベル変換回路の一例を例示する図である。

- 【図5】特許文献1のFig.3に基づく図である。

- 【図6】特許文献2の図5に基づく図である。

- 【図7】特許文献3の図1に基づく図である。

# 【発明を実施するための形態】

# [0016]

以下では、まず本発明の概要としてその一態様(mode)を説明し、つづいて実施形態について説明する。

# [0017]

本発明の一形態によれば、半導体装置に含まれるレベル変換回路(1)は、第1の節点(図1のN1)と第2の節点(図1のN2)との間に接続され、第1種別の膜厚のゲート 絶縁膜を有する第1のトランジスタ(図1のM5)と、第1の電源(図1のVDD2)と、信号を出力する出力端子(OUT)との間に接続され、前記第2の節点(N2)にゲートが接続され、第2種別の膜厚のゲート絶縁膜を有する第2のトランジスタ(例えば図1のM4)と、前記出力端子(OUT)と、第2の電源(VSS)との間に接続され、ゲートが前記第1の節点(N1)に接続された、前記第1種別の膜厚のゲート絶縁膜を有する第3のトランジスタ(図1のM3)を備えている。

10

20

30

40

#### [0018]

本発明の一形態によれば、レベル変換回路(1)は、前記第1の電源(VDD2)と前記第2の節点(N2)との間に接続され、ゲートが前記出力端子(OUT)に接続され、前記第2種別の膜厚のゲート絶縁膜を有する第4のトランジスタ(M6)をさらに備えている。

#### [0019]

本発明の一形態によれば、前記第1のトランジスタ(M5)のゲートは、前記第1の電源(VDD2)に接続されている。

#### [0020]

本発明の一形態によれば、レベル変換回路(1)は、第3の電源(VDD1)と前記第1の節点(N1)との間に接続され、前記第1種別の膜厚のゲート絶縁膜を有する第5のトランジスタ(M2)と、前記第1の節点(N1)と前記第2の電源(VSS)との間に接続され、前記第1種別の膜厚のゲート絶縁膜を有する第6のトランジスタ(M1)と、をさらに備え、前記第5及び第6のトランジスタのゲート同士は接続され、信号を入力する入力端子(IN)に接続されている。

#### [0021]

本発明の一形態によれば、前記第2の電源の電位は接地電位(VSS)であり、前記第1の電源(VDD2)、第3の電源(VDD1)の電位は前記第2の電源の電位よりも高い電位であり、前記第1の電源は、前記第3の電源よりも低電圧(VDD2<VDD1)とされる。

# [0022]

本発明の一形態によれば、前記第1種別の膜厚のゲート絶縁膜は、厚膜ゲート絶縁膜、前記第2種別の膜厚のゲート絶縁膜は、薄膜ゲート絶縁膜である。前記第1及び第3のトランジスタが第1導電型(例えばN型)であり、前記第2のトランジスタが第2導電型(例えばP型)であり、少なくとも前記第2のトランジスタ(M4)は、低電圧の閾値を有する。上記構成の本発明によれば、信号のハイレベル側を第3電源から第1の電源の電位にレベル変換するレベル変換回路において、第1の電源の低電圧化に対して、十分な動作マージを確保することができる。以下、図面を参照して、実施形態に即して詳細に説明する。

# [0023]

# <実施形態>

図1は、本発明の一実施形態のレベル変換回路の構成を例示する図である。図1を参照すると、レベル変換回路1は、第1の高電位側電源(電源端子、電源線)VDD1にソース端子が接続されたPMOSトランジスタM2と、低電位側電源(接地端子、接地線)VSSにソース端子が接続されたNMOSトランジスタM1と、を備えている。PMOSトランジスタM2のゲート端子とNMOSトランジスタM2のドレイン端子(パッド)に共通接続されている。また、PMOSトランジスタM2のドレイン端子とNMOSトランジスタM1のドレイン端子はノードN1(第1節点)に共通接続されている。NMOSトランジスタM1とPMOSトランジスタM2は、例えば耐圧を考慮して、ともに、厚膜のゲート絶縁膜を有する厚膜トランジスタからなる。

#### [0024]

レベル変換回路1は、ノードN1(第1節点)にソース端子が接続され、第2の高電位側電源VDD2にゲート端子が接続され、ノードN2(第2節点)にドレイン端子が接続され、ゲート絶縁膜が厚膜のNMOSトランジスタM5をさらに備えている。NMOSトランジスタM5の閾値は、低閾値電圧としてもよい。第2の高電位側電源VDD2と第1の高電位側電源VDD1の電源電圧は、VDD2<VDD1である。

# [0025]

レベル変換回路1は、第2の高電位側電源(電源端子、電源線)VDD2にソース端子が接続され、ゲート絶縁膜が薄膜のPMOSトランジスタM4と、低電位側電源VSSにソース端子が接続され、ゲート絶縁膜が厚膜のNMOSトランジスタM3と、をさらに備

10

20

30

20

30

40

50

えている。PMOSトランジスタM4のドレイン端子とNMOSトランジスタM3のドレイン端子は出力端子OUTに共通接続されている。PMOSトランジスタM4のゲート端子はノードN2に接続されている。NMOSトランジスタM3のゲート端子はノードN1に接続されている。薄膜PMOSトランジスタM4は、低閾値電圧のトランジスタである

# [0026]

さらに、レベル変換回路1は、第2の高電位側電源VDD2にソース端子が接続され、 ノードN2にドレイン端子が接続され、出力端子OUTにゲート端子が接続され、ゲート 絶縁膜が薄膜のPMOSトランジスタM6を備えている。

# [0027]

なお、図1において、MOSトランジスタの表記として、ゲートと反対側に小さな丸印を付したもの(例えばM4、M5)は、低閾値電圧であることを表しており、ゲート端子(ゲート電極)を表す線に対向する太線は厚膜ゲート絶縁膜を表している(例えばM1、M2、M3、M5)。

#### [0028]

図1において、NMOSトランジスタM1、M3、M5とPMOSトランジスタM2はいずれもゲート絶縁膜が厚膜(第1種別の厚さ)のトランジスタであるが、これらのトランジスタのゲート絶縁膜の膜厚toxは互いに同一であってもよいし、異なっていてもよい。また、PMOSトランジスタM4、M6はいずれもゲート絶縁膜が薄膜(第2種別の厚さ)のトランジスタであるが、PMOSトランジスタM4、M6のゲート絶縁膜の膜厚toxは同一であってもよいし、異なっていてもよい。また、薄膜のPMOSトランジスタM4、M6のゲート絶縁膜は、厚膜PMOSトランジスタM2のゲート絶縁膜の膜厚の比較において、その膜厚が薄く形成されていればよく、特段に薄いあるいは極薄であることは要しない(意味していない)。

#### [0029]

次に、図1に示したレベル変換回路の動作を説明する。端子INの信号がLowレベルからHighレベル(=VDD1)に変化すると、それまで非導通(オフ)状態のNMOSトランジスタM1が導通(オン)し、一方、それまでオン状態(導通状態)であったPMOSトランジスタM2は非導通となり(オフし)、ノードN1は、低電位側電源電圧(接地電位)VSSとなり、NMOSトランジスタM3はオン状態からオフに切り替わる。ノードN1が接地電位VSSとなると、ゲートに電源VDD2が印加されたNMOSトランジスタM5は、ゲート・ソース間電圧がVDD2となり、閾値電圧を超えるため、オンし、ノードN2(PMOSトランジスタM4のゲートノード)の電荷を引き抜く。このとき、出力端子(OUT)がHigh電位に立ち上がるまでの間、すなわち、PMOSトランジスタM6がオフするまでの間、ノードN2はPMOSトランジスタM6を介して電源VDD2側にプルアップされるが(すなわち、ノードN2は電源VDD2から充電されるが)、電源VDD2に接続するPMOSトランジスタM6と、NMOSトランジスタM5(及び、NMOSトランジスタM1)等の レシオ( はMOSトランジスタの利得係数)の調整等により、ノードN2の電荷を引き抜き、ノードN2をLowレベルに設定することが可能である。

#### [0030]

そして、ノードN2がLowレベルとなると、PMOSトランジスタM4が導通し、出力端子(OUT)は、電源電圧VDD2に立ち上がる。この結果、PMOSトランジスタM6はオフ状態となる。

# [0031]

次に、入力端子INの信号がLowレベルとなると、NMOSトランジスタM1はオフし、PMOSトランジスタM2がオンし、ノードN1は電源電圧VDD1となる。このため、NMOSトランジスタM3はオンし、出力端子(OUT)の電荷が低電位側電源VSSに引き抜かれ、出力端子(OUT)の電位はVSS(Lowレベル)に立ち下がる。ソース端子に電源電圧VDD1が印加されたNMOSトランジスタM5のドレイン端子(ノ

20

30

40

50

ードN2)は、最大VDD2-Vth(VthはNMOSトランジスタM5の閾値電圧)となる。このとき、出力端子(OUT)のLowへの遷移に応答してPMOSトランジスタM6がオンし、電位がVDD2-VthであるノードN2を、第2の高電位側電源VDD2から充電してVDD2にプルアップする。このため、PMOSトランジスタM4は確実にオフ状態となる。

# [0032]

特に制限されないが、図1において、例えば薄膜PMOSトランジスタM4の閾値電圧を・0・4、厚膜PMOSトランジスタM2の閾値電圧を・0・7、薄膜NMOSトランジスタ(図1には存在しない)の閾値電圧を0・4、厚膜NMOSトランジスタM2、M5の閾値電圧を0・6としてもよい。なお、NMOSトランジスタM5は耐圧を考慮して厚膜トランジスタとされているが、閾値電圧を下げた構成としてもよい。

# [0033]

図 2 に、図 1 の回路のシミュレーション結果を示し、併せて比較例のシミュレーション 結果を対比させて示す(動作温度は所定温度:例えば-35 等)。

#### [0034]

図4に、図2でシミュレーション対象とした比較例の回路構成を例示する。図4を参照 すると、第1の高電位側電源VDD1にソース端子が接続され、ゲート絶縁膜が厚膜のP MOSトランジスタM12と、低電位側電源VSSにソース端子が接続され、ドレイン端 子がPMOSトランジスタM12のドレイン端子に接続され、ゲート端子がPMOSトラ ンジスタM12のゲート端子と共通に入力端子(パッド)INに接続され、ゲート絶縁膜 が厚膜のNMOSトランジスタM11と、第2の高電位側電源VDD2にソース端子が接 続され、ゲート絶縁膜が厚膜のPMOSトランジスタM14と、低電位側電源VSSにソ ース端子が接続され、ドレイン端子がPMOSトランジスタM14のドレイン端子に接続 され、ゲート絶縁膜が厚膜のNMOSトランジスタM13と、を備えている。PMOSト ランジスタM14のゲート端子とNMOSトランジスタM13のゲート端子は共通接続さ れてPMOSトランジスタM12とNMOSトランジスタM11のドレイン端子の接続点 (ノードN11)に接続され、PMOSトランジスタM14とNMOSトランジスタM1 3のドレイン端子は共通接続されて出力端子(パッド)OUTに接続されている。VDD 1、VDD2系のトランジスタは、耐圧保護のため、膜厚トランジスタが用いられている 。VDD2の電源電圧の低下に対応するため、MOSトランジスタM13、M14をとも に低閾値電圧のトランジスタとしている。

#### [0035]

再び、図 2 を参照すると、図 1 、図 4 において、VDD1を1.7V、VDD2を0.7Vとしている。

# [0036]

入力信号は、図2の(a)に示すように、Lowレベル、Highレベルを0V、1.7Vとする矩形波(Highパルス)である。

# [0037]

図2の(b)は、図4において、NMOSトランジスタM11、M13を高閾値電圧、PMOSトランジスタM12、M14を低閾値電圧としている。なお、図4では、厚膜NMOSトランジスタM13は低閾値電圧であるが、(b)は、厚膜NMOSトランジスタM13を高閾値電圧とし、厚膜PMOSトランジスタM14を低閾値電圧としたときの出力端子OUTの電圧波形である。

### [0038]

図2の(c)は、(b)に対応して、図1の実施形態において、NMOSトランジスタM1、M3を高閾値電圧、PMOSトランジスタM4、M6を低閾値電圧としたときの出力端子OUTの電圧波形である。

# [0039]

図2の(b)、(c)に示すように、比較例と実施形態とも動作するが、(b)の比較例では、ゲート絶縁膜が膜厚のPMOSトランジスタM14の閾値電圧は、ゲート絶縁膜

# [0040]

これに対して、図1の実施形態では、ゲート絶縁膜が薄膜のPMOSトランジスタM4を用いており、閾値の低電圧化が困難な厚膜PMOSトランジスタを用いていないため、図2の(b)の比較例のような、出力端子OUTからの出力信号波形に立ち上がりの遅延は生じない。すなわち、図1において、入力端子INがLowからHighに遷移し、NMOSトランジスタM1がオンし、PMOSトランジスタM2がオフし、ノードN1の電荷がVSS側に引き抜かれ、ノードN1の電位(NMOSトランジスタM5がオン状態であるため、ノードN2の電位と等しい)が、VDD2-|Vtp2|(ただし、Vtp2は、図4の低閾値のPMOSトランジスタM14の閾値電圧)よりも低くなると、PMOSトランジスタM4がオンする。ここで、|Vtp2|<|Vtp1|であるため、PMOSトランジスタM4がオンする時間の遅延は、比較例よりも小さい。このため、図2の(c)に示すように、出力端子OUTの出力信号の立ち上がり波形には、図2の(b)のような遅れは生じない。

#### [0041]

図2の(d)は、図4において、NMOSトランジスタM11、M13を低閾値電圧、PMOSトランジスタM12、M14等を高閾値電圧としたときの出力端子OUTの電圧波形である。なお、図4の比較例では、PMOSトランジスタM14は低閾値電圧であるが、このシミュレーションでは厚膜NMOSトランジスタM13を低閾値電圧、厚膜PMOSトランジスタM14を高閾値電圧の組み合わせに対してシミュレーションを行っている。

# [0042]

図2の(e)は、図2の(d)に対応して、図1における閾値の設定として、例えば、NMOSトランジスタM3、M5等を低閾値電圧とし、PMOSトランジスタM4、M6等を高閾値電圧としたときの出力端子OUTの電圧波形である。ただし、図1において、薄膜PMOSトランジスタM4、M6の閾値は、図4の厚膜PMOSトランジスタM14の閾値よりも低電圧化が可能である。

# [0043]

(d)に示すように、図4の比較例では、入力信号のHighパルス期間に、ノードN1はLow電位となるが、VDD2が0.7V、PMOSトランジスタM14の閾値電圧Vtpが例えば・0.7Vのときは、PMOSトランジスタM14のゲート・ソースを置てVGSの絶対値が0.7よりも十分に大とならないため、PMOSトランジスタM14のゲート・ソース間電圧VGSが低いと、ソース・ドレイン間の抵抗(オン抵抗)は高くなる。さらに、高耐圧の厚膜PMOSトランジスタM14のソース・ドレイン間の抵抗(オン抵抗)は、薄膜のトランジスタのオン抵抗よりも高い。このため、入力信号がHighの期間中に、PMOSトランジスタM14による充電が十分に行われず、出力端子OUTはHighレベルに立ち上がらず、Highパルス期間の終わりに、わずかに0.1V程度にしか立ち上がらず、入力信号のLowへの遷移に応じて、VSS電位に戻っている。このように、図4の比較例の回路は動作しない。なお、図5、図6に示した特許文献1、2等の回路も、プルアップ用のPMOSトランジスタM22の影響により、出力端子からの出力信号波形はさらに悪化する。

# [0044]

10

20

30

これに対して、図1において、上記のように、閾値を設定した場合、図2の(e)に示すように、入力信号のHighパルスに対応して出力端子OUTの出力信号波形は、振幅0.7 VのHighパルスが出力される。このように、図1の実施形態において、PMOSトランジスタM4を高閾値電圧とした場合にも、適正に動作することが確認された。

# [0045]

図3は、本発明を適用した半導体装置の一実施形態を例示する図である。図3において、図7と同一の要素には同一の参照符号が付されている。以下では、図7と同一要素の説明は省略する。

# [0046]

図3に示すように、本実施形態に係る半導体装置は、テスト時に、各制御回路を制御するテストモード制御回路91と、テストモード制御回路91からの制御信号を受け、内部電源電圧(例えばVDD2)を生成する内部電源発生回路92を備えている。図1の実施形態のレベル変換回路は、VDD2をセルアレイ電源とし、VDD1(<VDD2)を駆動電源電圧としたとき、VDD2の振幅の信号をVDD1の振幅の信号に変換する任意の回路に適用される。例えばテストモード制御回路91、内部電源発生回路92に用いられる。

# [0047]

なお、上記の特許文献の開示を、本書に引用をもって繰り込むものとする。本発明の全開示(請求の範囲を含む)の枠内において、さらにその基本的技術思想に基づいて、実施形態ないし実施例の変更・調整が可能である。また、本発明の請求の範囲の枠内において種々の開示要素(各請求項の各要素、各実施例の各要素、各図面の各要素等を含む)の多様な組み合わせ乃至選択が可能である。すなわち、本発明は、請求の範囲を含む全開示、技術的思想にしたがって当業者であればなし得るであろう各種変形、修正を含むことは勿論である。

# 【符号の説明】

# [0048]

- 1 レベル変換回路

- 10、10b、10c、10d 半導体装置

- 11a、11b クロック端子

- 12a コマンドアドレス端子

- 1 2 b チップ選択端子

- 12c クロックイネーブル端子

- 14 データ入出力端子

- 15a、15b データストローブ端子

- 2.1 クロック入力回路

- 22 タイミング発生回路

- 23 分周回路

- 2.4 逓倍回路

- 25 記憶回路

- 3 1 コマンドアドレス入力回路

- 32 コマンドデコーダ

- 42 アドレスラッチ回路

- 5 1 ロウ系制御回路

- 52 カラム系制御回路

- 53 リードライト制御回路

- 54 モードレジスタ

- 61 ロウデコーダ

- 62 カラムデコーダ

- 6 3 センス回路

- 64 データアンプ

30

20

10

40

70 メモリセルアレイ

8 1 データ入出力回路

81R データ出力回路

81W データ入力回路

82 ストローブ回路

91 テストモード制御回路

9 2 内部電源発生回路

100 遅延調整回路

200 測定回路

IN 入力端子(パッド)

OUT 出力端子(パッド)

M 0 、 M 1 、 M 3 、 M 5 、 M 1 1 、 M 1 3 、 M 1 9 、 M 2 1 N M O S トランジスタ M 2 、 M 4 、 M 6 、 M 1 2 、 M 1 4 、 M 2 2 、 M 2 0 、 M 2 2 P M O S トランジスタ N 1 、 N 2 、 N 1 1 ノード (節点)

【図1】 【図2】

【図3】

# 【図5】 【図6】

# 【図7】

# フロントページの続き

(51)Int.Cl. F I テーマコード (参考)

H 0 3 K 19/0185 (2006.01)

F ターム(参考) 5F038 BE07 BH15 CD02 CD05 DF01 DF05 DT02 DT09 DT15 EZ20

5F083 AD00 GA11 ZA07 ZA08

5J056 AA11 BB12 BB18 CC21 DD13 DD29 EE07 GG09 KK01

5M024 AA02 AA37 AA49 BB03 BB30 BB33 BB34 DD38 DD58 JJ03

JJ04 JJ58 JJ59 MM04 PP01 PP02 PP03 PP07