## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2020-77075 (P2020-77075A)

(43) 公開日 令和2年5月21日(2020.5.21)

(51) Int.Cl. F I テーマコード (参考)

**GO 6 F** 12/06 (2006.01) GO 6 F 12/06 5 2 2 D 5 B 1 6 O GO 6 F 12/1027 (2016.01) GO 6 F 12/1027 1 2 O 5 B 2 O 5

審査請求 未請求 請求項の数 14 OL (全 21 頁)

(21) 出願番号 特願2018-208545 (P2018-208545) (22) 出願日 平成30年11月6日 (2018.11.6)

(出願人による申告) 平成28年度 国立研究開発法人新エネルギー・産業技術総合開発機構「1oT推進のための横断技術開発プロジェクト/高速大容量ストレージデバイス・システムの研究開発」委託研究、産業技術力強化法第19条の適用を受ける特許出願

(71) 出願人 000003078

株式会社東芝

東京都港区芝浦一丁目1番1号

(74)代理人 110002147

特許業務法人酒井国際特許事務所

(72)発明者 城田 祐介

東京都港区芝浦一丁目1番1号 株式会社

東芝内

(72) 発明者 金井 達徳

東京都港区芝浦一丁目1番1号 株式会社

東芝内

Fターム(参考) 5B160 MM03

5B205 MM51 VV03

(54) 【発明の名称】情報処理装置、情報処理方法、およびプログラム

# (57)【要約】

【課題】複数種類のメモリの使い分けに用いる情報を効率よく提供する。

【解決手段】情報処理装置10は、取得部12Aと、導出部12Cと、決定部12Dと、を備える。取得部12 Aは、処理回路12の動作統計情報42Aを取得する。導出部12Cは、動作統計情報42Aから処理回路12のメモリアクセス特性42Bを導出するための予測モデル20に基づいて、取得した動作統計情報42Aからメモリアクセス特性42Bを導出する。決定部12Dは、導出したメモリアクセス特性42Bに基づいて、第1記憶部14Aより処理回路12によるアクセス速度が遅い第2記憶部14Bのデータを第1記憶部14Aへ転送し、第1記憶部14A内の該データにアクセスする第1アクセス方式、または、第2記憶部14B内のデータにアクセスする第2アクセス方式、の何れかのアクセス方式を決定する。

【選択図】図3

# 【特許請求の範囲】

## 【請求項1】

処理回路の動作統計情報を取得する取得部と、

前記動作統計情報から前記処理回路のメモリアクセス特性を導出するための予測モデルに基づいて、取得した前記動作統計情報から前記メモリアクセス特性を導出する導出部と

導出した前記メモリアクセス特性に基づいて、第1記憶部より前記処理回路によるアクセス速度が遅い第2記憶部のデータを前記第1記憶部へ転送し、前記第1記憶部内の該データにアクセスする第1アクセス方式、または、前記第2記憶部内のデータにアクセスする第2アクセス方式、の何れかのアクセス方式を決定する決定部と、

を備える情報処理装置。

## 【請求項2】

決定された前記アクセス方式に応じて、前記データの前記第2記憶部から前記第1記憶部への転送および前記第1記憶部内の該データへのアクセス、または、前記第2記憶部内のデータへのアクセス、を実行する実行部、

を備える請求項1に記載の情報処理装置。

#### 【請求項3】

前記動作統計情報は、

前記処理回路が実行中のアプリケーションに割当てられた物理メモリサイズ、および、 TLB(Translation Lookaside Buffer)ミスに関する動 作統計情報、の少なくとも一方を含む、

請求項1または請求項2に記載の情報処理装置。

### 【請求項4】

前記メモリアクセス特性は、

前記処理回路が単位期間あたりに使用したメモリサイズを示す、

請求項1~請求項3の何れか1項に記載の情報処理装置。

## 【請求項5】

前記決定部は、

導出した前記メモリアクセス特性が第1閾値より大きい場合、前記第2アクセス方式を 決定し、該メモリアクセス特性が前記第1閾値以下の場合、前記第1アクセス方式を決定 する、

請求項4に記載の情報処理装置。

# 【請求項6】

第1閾値は、前記処理回路が利用可能な、前記第1記憶部のサイズ以上の値である、請求項5に記載の情報処理装置。

# 【請求項7】

前記決定部は、

取得した前記動作統計情報に関する1または複数のアプリケーションの各々に割当てられた物理メモリサイズの合計値に対する、前記メモリアクセス特性の比率が、第2閾値より大きい場合、前記第2アクセス方式を決定し、前記第2閾値以下の場合、前記第1アクセス方式を決定する、

請求項1~請求項3の何れか1項に記載の情報処理装置。

# 【請求項8】

前記第2閾値は、前記合計値のN分の1である(Nは、2以上の整数)、請求項7に記載の情報処理装置。

#### 【請求項9】

前記第1アクセス方式を決定した場合、

前記第1記憶部の利用可能なメモリサイズを変更する変更部、

を備える、請求項1~請求項8の何れか1項に記載の情報処理装置。

# 【請求項10】

10

20

30

40

前記動作統計情報と前記メモリアクセス特性との対応を示す教師データを複数含む教師データセットを用いて、前記予測モデルを学習する学習部、

を備える、請求項1~請求項9の何れか1項に記載の情報処理装置。

#### 【請求項11】

前記教師データは、アプリケーションの命令単位ごとの、前記動作統計情報と前記メモリアクセス特性との対応を示す、

請求項10に記載の情報処理装置。

# 【請求項12】

前記学習部は、学習用のアプリケーションを少なくとも2回実行し、一方の回の該アプリケーションの実行によって前記動作統計情報を取得し、他方の回の該アプリケーションの実行によって前記メモリアクセス特性を取得し、該アプリケーションの命令単位ごとに、取得した前記動作統計情報と取得した前記メモリアクセス特性との対応を示す前記教師データを生成する、

請求項11に記載の情報処理装置。

### 【請求項13】

処理回路の動作統計情報を取得するステップと、

前記動作統計情報から前記処理回路のメモリアクセス特性を導出するための予測モデルに基づいて、取得した前記動作統計情報から前記メモリアクセス特性を導出するステップと、

導出した前記メモリアクセス特性に基づいて、第1記憶部より前記処理回路によるアクセス速度が遅い第2記憶部のデータを前記第1記憶部へ転送し、前記第1記憶部内の該データにアクセスする第1アクセス方式、または、前記第2記憶部内のデータにアクセスする第2アクセス方式、の何れかのアクセス方式を決定するステップと、

を含む情報処理方法。

## 【請求項14】

処理回路の動作統計情報を取得するステップと、

前記動作統計情報から前記処理回路のメモリアクセス特性を導出するための予測モデルに基づいて、取得した前記動作統計情報から前記メモリアクセス特性を導出するステップと、

導出した前記メモリアクセス特性に基づいて、第1記憶部より前記処理回路によるアクセス速度が遅い第2記憶部のデータを前記第1記憶部へ転送し、前記第1記憶部内の該データにアクセスする第1アクセス方式、または、前記第2記憶部内のデータにアクセスする第2アクセス方式、の何れかのアクセス方式を決定するステップと、

をコンピュータに実行させるためのプログラム。

# 【発明の詳細な説明】

# 【技術分野】

#### [00001]

本発明の実施形態は、情報処理装置、情報処理方法、およびプログラムに関する。

## 【背景技術】

# [0002]

MRAM(Magnetoresistive Random Access Memory)、ReRAM(Resistive RAM)、PCM(Phase-Change Memory)などの各種のストレージクラスメモリ(SCM)が開発されている。SCMは、DRAM(Dynamic Random Access Memory)に比べてアクセス速度は遅いが、集積度が高い。一方、DRAMは、SCMに比べて集積度は低いが、アクセス速度が速い。このため、複数種類のメモリを搭載したシステムの場合、これらのメモリを使い分けて用いる必要がある。

## [0003]

しかし、従来では、複数の種類のメモリの使い分けに用いる情報が管理されておらず、 また、この情報を収集する手段を有していなかった。このため、従来では、複数種類のメ 10

20

30

40

モリの使い分けに用いる情報を効率よく提供することは困難であった。

### 【先行技術文献】

#### 【非特許文献】

#### [0004]

【非特許文献1】R. F. Freitas and W. W. Wilcke, "Storage-class Memory: The Next Storage System Technology", IBM Journal of Research and Development Vol.52 No.4, pp.439-447, 2008.

#### 【発明の概要】

【発明が解決しようとする課題】

## [0005]

本発明が解決しようとする課題は、複数種類のメモリの使い分けに用いる情報を効率よく提供することができる、情報処理装置、情報処理方法、およびプログラムを提供することである。

## 【課題を解決するための手段】

# [0006]

実施形態の情報処理装置は、取得部と、導出部と、決定部と、を備える。取得部は、処理回路の動作統計情報を取得する。導出部は、前記動作統計情報から前記処理回路のメモリアクセス特性を導出するための予測モデルに基づいて、取得した前記動作統計情報から前記メモリアクセス特性を導出する。決定部は、導出した前記メモリアクセス特性に基づいて、第1記憶部より前記処理回路によるアクセス速度が遅い第2記憶部のデータを前記第1記憶部へ転送し、前記第1記憶部内の該データにアクセスする第1アクセス方式、または、前記第2記憶部内のデータにアクセスする第2アクセス方式、の何れかのアクセス方式を決定する。

# 【図面の簡単な説明】

## [0007]

- 【図1】情報処理装置の構成の一例を示す模式図。

- 【図2】物理アドレス空間の模式図。

- 【図3】処理回路の機能ブロック図。

- 【図4】予測モデルの学習の説明図。

- 【図5】動作統計情報とメモリアクセス特性との関係の説明図。

- 【図 6 A 】動作統計情報の模式図。

- 【図6B】メモリアクセス特性の模式図。

- 【図7】導出部および決定部の処理の説明図。

- 【図8】アクセス方式の決定の説明図。

- 【図9】情報処理の手順のフローチャート。

- 【図10】情報処理の手順のフローチャート。

# 【発明を実施するための形態】

# [0008]

以下に添付図面を参照して、本実施の形態の詳細を説明する。

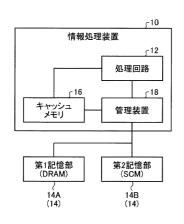

#### [0009]

図1は、本実施の形態の情報処理装置10の構成の一例を示す模式図である。情報処理 装置10は、処理回路12と、キャッシュメモリ16と、管理装置18と、を備える。情 報処理装置10のメモリバスには、記憶部14が接続されている。

### [0010]

処理回路12とキャッシュメモリ16、処理回路12と管理装置18、および、キャッシュメモリ16と管理装置18、の各々は、データや信号を授受可能に接続されている。 処理回路12および管理装置18と記憶部14とは、データや信号を授受可能に接続されている。 10

20

\_\_\_

30

40

#### [0011]

処理回路12は、1または複数のプロセッサを有する。プロセッサは、例えば、CPU(Central Processing Unit)である。プロセッサは、1または複数のCPUコアを含んでいてもよい。処理回路12は、1または複数のアプリケーションプログラムの実行に応じて、管理装置18を介して、記憶部14からのデータ読出しや、記憶部14へのデータ書込みを行う。

# [0012]

なお、以下では、アプリケーションプログラムを、単に、アプリケーション、と称して説明する場合がある。また、記憶部14からのデータ読出および記憶部14へのデータ書込みを総称して説明する場合には、記憶部14へのアクセス、と称して説明する場合がある。

## [0013]

処理回路12および管理装置18は、記憶部14に記憶されているデータをキャッシュ メモリ16に一時的に記憶し、処理に用いる。

### [0014]

記憶部14は、処理回路12による作業領域として用いられるメインメモリである。本 実施の形態の情報処理装置10は、複数種類の記憶部14を備える。すなわち、本実施の 形態の情報処理装置10は、複数種類の記憶部14を、メインメモリとして用いる。

## [0015]

複数種類の記憶部14は、処理回路12によるアクセス速度が互いに異なる。なお、以下では、処理回路12によるアクセス速度を、単にアクセス速度と称して説明する場合がある。また、アクセス速度は、アクセス遅延とも呼ばれることもある。アクセス速度が速いというのは、アクセス遅延時間が短いことである。

#### [0016]

本実施の形態では、情報処理装置10は、アクセス速度の異なる複数種類の記憶部14として、第1記憶部14Aと、第2記憶部14Bと、を備える。なお、情報処理装置10は、3種類以上の記憶部14を備えた構成であってもよい。

# [0017]

第1記憶部14Aは、第2記憶部14Bに比べてアクセス速度が速い。また、本実施の 形態では、第1記憶部14Aは、第2記憶部14Bより集積度が低い。

# [0018]

第1記憶部14Aは、例えば、揮発性メモリである。具体的には、第1記憶部14Aは、DRAM(Dynamic Random Acces Memory)である。なお、第1記憶部14Aは、DRAMと同程度に高速アクセスが可能な、MRAM(Magnetoresistive Random Acces Memory)等の不揮発メモリであってもよい。

## [0019]

一方、第2記憶部14Bは、第1記憶部14Aに比べてアクセス速度が遅い。また、本実施の形態では、第2記憶部14Bは、第1記憶部14Aより集積度が高い。すなわち、第2記憶部14Bは、第1記憶部14Aより容量が大きい。

#### [0020]

第2記憶部14Bは、例えば、不揮発性メモリである。具体的には、第2記憶部14Bは、DRAMより大容量な大容量高速不揮発メモリ(Non-volatile Memory)である。

# [0021]

更に具体的には、第2記憶部14Bは、MRAM、PCM(Phase Change Memory)、PRAM(Phase Random Access Memory)、PCRAM(Phase Change Random Access Memory)、ReRAM(Resistance Change Random Access Memory)、FeRAM(Ferroelectric Random Acce

10

20

30

40

ss Memory)、3DXPointまたはMemristorなどである。

## [0022]

また、第2記憶部14Bは、いわゆるストレージクラスメモリ(SCM)と呼ばれるメモリであってもよい。また、第2記憶部14Bは、複数の半導体装置を1つの基板または筐体等に設けたモジュールであってもよい。

# [0023]

本実施の形態では、第1記憶部14AがDRAMであり、第2記憶部14BがSCMである場合を、一例として説明する。なお、第1記憶部14Aのアクセス速度が第2記憶部14Bより速ければよく、これらの組合せは、第1記憶部14AがDRAMであり第2記憶部14BがSCMである形態に限定されない。例えば、第1記憶部14AがMRAMであり、第2記憶部14BがReRAMであってもよい。

## [0024]

なお、第1記憶部14Aおよび第2記憶部14Bを総称して説明する場合には、単に、記憶部14と称して説明する。

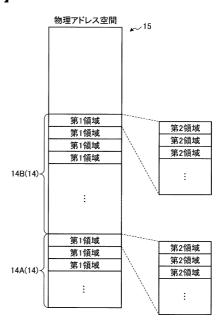

#### [0025]

記憶部14は、複数の第1領域を含む。第1領域は、複数の第2領域を含む。言い換えると、本実施の形態では、処理回路12および管理装置18が、第1記憶部14Aおよび第2記憶部14Bを、第1領域毎に管理すると共に、第1領域内の第2領域ごとに管理する。

# [0026]

図2は、処理回路12から見た物理アドレス空間を示す模式図である。

#### [0027]

図2に示すように、第1記憶部14Aおよび第2記憶部14Bは、それぞれ、複数の第1領域を含む。

## [0028]

第1領域は、例えば、処理回路12によるデータの管理単位、あるいは、処理回路12上で動作するオペレーティングシステムによるデータの管理単位(例えば、ページ)である。ページは例えば4KBなどである。言い換えると、第1領域は、第1記憶部14Aと第2記憶部14Bとの間でデータを転送するときの、転送単位である。なお、第1領域は、処理回路12によるデータの管理単位の所定数倍の単位などであってもよい。本実施の形態では、第1領域が、ページに相当する場合を、一例として説明する。

# [0029]

第2領域は、第1領域より小さい領域である。例えば、第2領域は、処理回路12による記憶部14に対するアクセスに伴うデータの書き換え単位である。すなわち、第2領域は、処理回路12によるデータのアクセス単位である。具体的には、第2領域は、キャッシュラインと呼ばれる単位である。キャッシュラインは、キャッシュメモリ16に対するデータの書き換え単位に対応する。すなわち、処理回路12からのメモリアクセス要求を受けた管理装置18は、キャッシュラインの単位で、第1記憶部14Aまたは第2記憶部14Bにアクセスする。

# [0030]

キャッシュラインは、例えば、64バイトである。なお、第2領域は、キャッシュラインよりも小さい単位(例えば、バイト単位)であってもよい。また、第2領域は、キャッシュラインのサイズの所定数倍の単位などであってもよい。

## [0031]

本実施の形態では、処理回路12および管理装置18は、図2に示す物理アドレス空間15にマッピングされた第1記憶部14Aおよび第2記憶部14B内の領域を、第1領域のサイズ(例えば、ページサイズ)に区切って管理する。そして、処理回路12および管理装置18は、ページテーブルを用いて論理アドレスから物理アドレスに変換することで、仮想記憶を実現する。

# [0032]

20

10

30

図 1 に戻り、説明を続ける。管理装置 1 8 は、処理回路 1 2 による、複数種類の記憶部 1 4 (第 1 記憶部 1 4 A、第 2 記憶部 1 4 B)に対するアクセスを管理する。管理装置 1 8 は、メモリ管理ユニット(M M U: Memory Management Unit)などと称される場合がある。管理装置 1 8 はメモリコントローラなどであってもよい。

管理装置18は、処理回路12から受付けたメモリアクセス要求を処理する。メモリアクセス要求は、処理回路12から記憶部14に対するアクセス要求である。メモリアクセス要求は、記憶部14へのデータ書込み、または記憶部14からのデータ読出しを示す。メモリアクセス要求は、アクセス対象の記憶部14の第1領域のアドレス情報および第2領域のアドレス情報を含む。これらのアドレス情報は、論理アドレスによって表される。【0034】

管理装置18は、処理回路12から受付けたメモリアクセス要求によって示されるアクセス対象のデータがキャッシュメモリ16に格納されていない場合、記憶部14ヘアクセスする。この場合、管理装置18は、処理回路12から受付けたメモリアクセス要求によって示される、アクセス対象の記憶部14における第1領域内の第2領域にアクセスする。そして、管理装置18は、アクセスした該第2領域に対して、メモリアクセス要求によって示される処理(書込みや読出し)を実行する。

# [0035]

[0033]

具体的には、処理回路12から受付けたメモリアクセス要求が特定の第2領域への書込みを示す場合がある。この場合、管理装置18は、メモリアクセス要求に示される、アクセス対象の記憶部14における、アクセス対象の第1領域内の第2領域に、メモリアクセス要求に示されるデータを書込む。また、処理回路12から受付けたメモリアクセス要求が特定の第2領域からのデータ読出しを示す場合がある。この場合、管理装置18は、メモリアクセス要求に示される、アクセス対象の記憶部14における、アクセス対象の第1領域内の第2領域からデータを読出し、キャッシュメモリ16に格納するとともに、処理回路12へ出力する。

## [0036]

次に、処理回路12について詳細を説明する。上述したように、処理回路12は、1または複数のアプリケーションの実行に応じて、管理装置18を介して、記憶部14へのアクセスを行う。

# [0037]

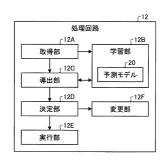

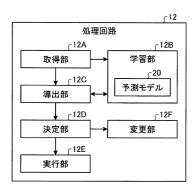

図3は、処理回路12の機能ブロック図の一例である。処理回路12は、取得部12Aと、学習部12Bと、導出部12Cと、決定部12Dと、実行部12Eと、変更部12Fと、を備える。

# [0038]

取得部12A、学習部12B、導出部12C、決定部12D、実行部12E、および変更部12Fの少なくとも1つは、CPUなどのプロセッサにプログラムを実行させること、すなわちソフトウェアにより実現してもよい。また、取得部12A、学習部12B、導出部12C、決定部12D、実行部12E、および変更部12Fの少なくとも1つは、専用のIC(Integrated Circuit)などのハードウェアにより実現してもよい。また、取得部12A、学習部12B、導出部12C、決定部12D、実行部12E、および変更部12Fの少なくとも1つは、ソフトウェアおよびハードウェアを併用して実現してもよい。複数のプロセッサを用いる場合、各プロセッサは、これらの取得部12A、学習部12B、導出部12C、決定部12D、実行部12E、および変更部12Fのうち1つを実現してもよいし、各部のうち2以上を実現してもよい。

#### [0039]

取得部12Aは、処理回路12の動作統計情報を取得する。

#### [0040]

動作統計情報とは、処理回路12の動作に関する情報の統計値である。詳細には、動作統計情報は、処理回路12が1または複数のアプリケーションを実行時の、動作に関する

10

20

30

40

情報の統計値である。動作に関する情報の統計値とは、単位期間 T あたりの、動作に関する情報を示す。単位期間 T は、予め設定すればよい。動作統計情報は、管理装置 1 8 やキャッシュメモリ 1 6 や情報処理装置 1 0 の動作に関する情報の統計値であってもよい。動作統計情報は、例えば、プロセッサが備える、ハードウェアイベントを測定する性能カウンタにより収集される。動作統計情報は、例えば、OSが管理する、情報処理装置の状態やOS内部の状態を示す情報(例えば、OS内部のイベント発生回数の統計情報)全般であってもよい。

# [0041]

具体的には、動作統計情報は、性能カウンタなどで収集される、単位期間Tあたりの、TLB(Translation Lookaside Buffer)ミスの回数、TLBミスに関する動作統計情報、キャッシュメモリの各階層(L1キャッシュ、L2キャッシュ、L3キャッシュ、LLC(Last Level Cache)など)のキャッシュミスの回数、キャッシュミスのミスに関する動作統計情報、記憶部14への書込回数、記憶部14からの読出回数、STLB(Secondary level TLB)ミスの回数、STLBミスに関する動作統計情報のなどのハードウェアイベントのうち、1または複数によって表される。動作統計情報には、さらに、OSが管理する、当該実行期間に実行されているアプリケーションに当該実行期間中に割当てられている物理メモリサイズ(つまりアプリケーションの実行中のいずれかのタイミングでアクセスされる可能性があるメモリのサイズ)なども含まれていてもよい。なお、動作統計情報は、これらに限定されない。

# [0042]

取得部12Aは、公知の方法で、処理回路12の動作統計情報を取得すればよい。例えば、取得部12Aは、処理回路12に設けられた性能カウンタから、単位期間Tごとの動作統計情報を順次取得すればよい。性能カウンタは、例えば、Inte1プロセッサのパフォーマンスモニタリングカウンタ(Performance Monitoring Counter)などであるが、これに限定されない。取得部12Aは、性能カウンタと一体的に構成してもよい。また、取得部12Aと性能カウンタとを、別体として構成してもよい。本実施の形態では、取得部12Aと性能カウンタとを、別体として構成する形態を一例として説明する。

# [0043]

学習部 1 2 B は、教師データを複数含む教師データセットを用いて、予測モデル 2 0 を 学習する。

# [0044]

予測モデル20は、動作統計情報からメモリアクセス特性を導出するためのモデルである。予測モデル20は、学習によって生成される、学習モデルである。

#### [0045]

メモリアクセス特性とは、第1記憶部14Aおよび第2記憶部14Bに対する、処理回路12によるアクセスの特性を示す。

# [0046]

例えば、メモリアクセス特性は、処理回路12がアプリケーション実行中に単位期間Tあたりに使用したメモリサイズによって表される。詳細には、メモリアクセス特性は、例えば、処理回路12がアプリケーション実行中に単位期間Tあたりに記憶部14やキャッシュメモリ16上のデータに対してロード命令とストア命令を発行した場合、そのデータの合計サイズである。具体的には、処理回路12がアプリケーション実行中において、単位期間TあたりNページに対してアクセスしたと想定する(Nは1以上の整数)。この場合、1ページの容量が4Kバイトとした場合、メモリアクセス特性は、『N『に、1ページの容量である』4Kバイト『を乗算した結果(N×4K)によって表される。これは、一般に、ワーキングセットサイズなどとも呼ばれることもある。なお、メモリサイズは、処理回路12が記憶部14あるいは記憶部14のデータをキャッシュするキャッシュメモリ16に対してアクセスしたデータを格納するページのページ数(第1領域の数)で表し

10

20

30

40

てもよい。

## [0047]

学習部12Bは、動作統計情報を入力としメモリアクセス特性を出力とする予測モデル20を、教師データセットを用いて学習する。

#### [0048]

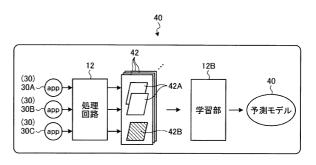

図4は、予測モデル20の学習の説明図である。教師データセット40は、複数の教師データ42を含む。教師データ42は、単位期間Tごとに生成される。教師データ42は、動作統計情報42Aと、メモリアクセス特性42Bと、を含む、なお、1つの教師データ42には、1または複数の動作統計情報42Aが含まれる。また、1つの教師データ42には、1または複数の動作統計情報42Aに対応する1つの正解情報として、1つのメモリアクセス特性42Bが含まれる。

## [0049]

処理回路12は、予め、教師データセット40を用意する。例えば、処理回路12は、1または複数の学習用のアプリケーション30(例えば、アプリケーション30A、アプリケーション30B、アプリケーション30C)を実行する。そして、処理回路12は、アプリケーション30を実行中における1または複数の動作統計情報42Aとメモリアクセス特性42Bとの組からなる教師データ42を、単位期間Tごとに生成する。この処理により、処理回路12は、予め、複数の教師データ42を含む教師データセット40を用意する。

# [0050]

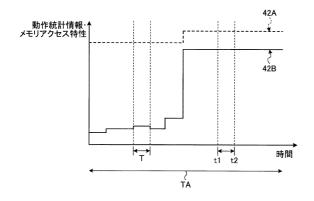

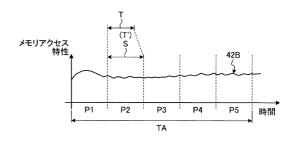

図 5 は、学習用のアプリケーション 3 0 の実行期間TAにおける、動作統計情報 4 2 A とメモリアクセス特性 4 2 B との関係の一例を示す説明図である。図 5 に示すグラフの縦軸は、動作統計情報またはメモリアクセス特性を示す。図 5 に示すグラフの横軸は、時間を示す。なお、図 5 には、動作統計情報 4 2 A が実行中のアプリケーションに割当てられた物理メモリサイズを示し、メモリアクセス特性 4 2 B が、処理回路 1 2 がアプリケーション実行中に単位期間Tあたりに使用したメモリサイズを示す場合を、一例として示した

# [0051]

処理回路12が、学習用のアプリケーション30を実行したときの、動作統計情報42 A およびメモリアクセス特性42Bの時間経過に伴う推移が、図5に示す推移を示したと想定する。この場合、学習部12Bは、単位期間Tごとの、動作統計情報42Aとメモリアクセス特性42Bとの対応を、単位期間Tごとの教師データ42として生成すればよい。なお、隣接するタイミングの教師データ42の単位期間Tは、一部が重複するタイミングであってもよく、また、互いに非重複のタイミングであってもよい。

# [0052]

学習部12Bは、性能カウンタから取得部12Aを介して、単位期間Tごとの動作統計情報42Aを取得することで、単位期間Tの教師データ42の生成に用いればよい。

# [0053]

また、学習部12Bは、教師データ42に用いる単位期間Tごとのメモリアクセス特性42Bを、以下の方法により取得すればよい。

### [0054]

詳細には、学習部12Bは、単位期間Tの最初のタイミング(例えば、t1)で、処理回路12に予めインストールされたOS(オペレーティングシステム)が管理するページテーブルの一部をリセットする。詳細には、学習部12Bは、ページテーブルの全てのページのアクセス済フラグを"0"として"アクセス未"とすることで、ページテーブルをリセットする。次に、学習部12Bは、該単位期間Tの区間の終了タイミング(例えば、t2)に、該ページテーブルにおけるアクセス済フラグ("1"となっているフラグ)を計数する。この計数処理により、学習部12Bは、単位期間Tに処理回路12によってアクセスされたページ数を求める。そして、学習部12Bは、該ページ数(N)に、1ページの容量である"4Kバイト"を乗算した結果(N×4K)を、該単位期間Tのメモリア

10

20

30

40

クセス特性42Bとして取得する。

## [0055]

そして、学習部12Bは、単位期間Tごとに、上記処理を実行する。そして、学習部1 2Bは、単位期間Tごとに取得した、動作統計情報42Aとメモリアクセス特性42Bと の対応を示す教師データ42を生成する。

### [0056]

ここで、上述したように、学習部12Bは、性能カウンタから取得部12Aを介して動作統計情報42Aを取得する。このため、学習部12Bは、学習用のアプリケーション30の実行中に、リアルタイムで動作統計情報42Aを取得可能である。一方、メモリアクセス特性42Bの取得には、学習部12Bは、ページテーブルのリセット、アクセス済フラグの計数、メモリアクセス特性42Bの計算、といった処理を、単位期間Tごとに実行する必要がある。このため、学習部12Bは、学習用のアプリケーション30の実行中に、リアルタイムでメモリアクセス特性42Bを取得することは困難な場合がある。また、ページテーブルのリセット、アクセス済フラグの計数、メモリアクセス特性42Bの計算、といった処理自体が、動作統計情報42Aに影響を与えてしまう(アプリケーションのみを実行した場合の動作統計情報42Aに対して大きく変化してしまう)可能性もあるため、それを回避するのが望ましい。

# [0057]

そこで、本実施の形態では、処理回路12は、学習用のアプリケーション30を2回実行する。そして、学習部12Bは、1回目および2回目の内の一方の回のアプリケーション30の実行時に動作統計情報42Aを取得し、他方の回のアプリケーション30の実行時にメモリアクセス特性42Bを取得する。そして、学習部12Bは、単位期間Tに対応する、アプリケーション30の命令単位ごとに、動作統計情報42Aとメモリアクセス特性42Bとの対応を示す教師データ42を生成する。

#### [0058]

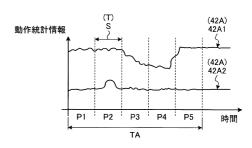

図6Aは、学習用のアプリケーション30を実行したときの、動作統計情報42Aの一例を示す模式図である。図6Aには、動作統計情報42Aとして、TLBミスに関する動作統計情報42A1と、実行中のアプリケーションに割当てられた物理メモリサイズ42A2と、を一例として示した。なお、図6Aに示すグラフの縦軸は、動作統計情報を示し、横軸は、時間を示す。

# [0059]

図6Aに示すように、処理回路12が、学習用のアプリケーション30を実行したときの、時間経過に伴う動作統計情報42Aの推移が、図6Aに示す推移を示したと想定する。そして、学習部12Bは、単位期間Tを、該アプリケーション30が命令単位Sを実行する期間と定める。命令単位Sは、例えば、10万回である。なお、命令単位Sの命令回数は、予め設定すればよく、10万回に限定されない。

#### [0060]

この場合、学習部12Bは、アプリケーション30の命令単位Sごとの動作統計情報4 2Aを、性能カウンタから取得することで、命令単位Sごと(すなわち、単位期間Tごと )の動作統計情報42Aを取得する。例えば、学習用のアプリケーション30を実行した 期間TAを、過去から未来に向かって、命令単位Sごとに、フェーズP1、フェーズP2 、フェーズP3、フェーズP4、フェーズP5に分割して管理すると想定する。この場合 、学習部12Bは、各フェーズ(フェーズP1~フェーズP5)の各々ごとの、動作統計 情報42Aを取得する。

# [0061]

次に、学習部12Bは、同じ学習用のアプリケーション30を再度実行し、命令単位Sごとのメモリアクセス特性42Bを取得する。

## [0062]

図 6 B は、教師データ 4 2 用の動作統計情報 4 2 A の取得時と同じ学習用のアプリケーション 3 0 を実行したときの、メモリアクセス特性 4 2 B の一例を示す模式図である。図

10

20

30

40

6 Bには、メモリアクセス特性 4 2 B として、処理回路 1 2 が単位期間 T あたりに使用したメモリサイズを一例として示した。なお、図 6 B に示すグラフの縦軸は、メモリアクセス特性を示し、横軸は、時間を示す。

#### [0063]

学習部12Bは、単位期間Tに相当する命令単位Sごとに、ページテーブルのリセット、アクセス済フラグの計数、メモリアクセス特性42Bの計算、を実行する。この処理により、学習部12Bは、命令単位Sごとの、メモリアクセス特性42Bを取得する。このため、学習部12Bは、フェーズ(フェーズ P 1 ~フェーズ P 5 )の各々の命令単位Sごとの、メモリアクセス特性42Bを取得する。

#### [0064]

そして、学習部12Bは、学習用のアプリケーション30の命令単位Sごとの、動作統計情報42Aとメモリアクセス特性42Bとの対応を示す、教師データ42を生成すればよい。

## [0065]

ここで、学習部 1 2 B が、命令単位 S ごとに、ページテーブルのリセット、アクセス済フラグの計数、メモリアクセス特性 4 2 B の計算、を実行するため、これらの実行に要する時間は、単位期間 T より長い期間 T 'となる場合がある。

### [0066]

しかし、本実施の形態では、学習部12Bが、動作統計情報42Aをリアルタイムで取得するときの単位期間Tに相当する命令単位Sを基準として、該命令単位Sごとのメモリアクセス特性42Bを取得する。このため、学習部12Bは、処理回路12が実際にアプリケーション30を実行したときの、単位期間Tごとの動作統計情報42Aとメモリアクセス特性42Bとの対応を示す教師データ42を、精度良く生成することができる。

#### [0067]

図4に戻り説明を続ける。そして、学習部12Bは、複数の教師データ42を含む教師データセット40を用いて、動作統計情報42Aからメモリアクセス特性42Bを導出するための予測モデル20を学習する。

### [0068]

学習部  $1 \ 2 \ B$  は、公知の学習アルゴリズムを用いて、予測モデル  $2 \ 0$  を学習すればよい。学習アルゴリズムは、例えば、線形回帰、k 近傍法(KNN:K-NearestNeighbor algorithm)、サポートベクターマシン、Random Forest などであるが、これらに限定されない。

# [0069]

学習部12Bは、予め予め定めたタイミング毎に、教師データセット40に含まれる複数の教師データ42を用いて、予測モデル20を学習すればよい。また、例えば、学習部12Bは、新たな教師データ42が教師データセット40に登録されるごとに、予測モデル20を学習してもよい。教師データ42登録は、任意のタイミングで実行すればよい。

# [0070]

また、学習部 1 2 B は、新たな教師データ 4 2 を含む教師データセット 4 0 を用いて新たな予測モデル 2 0 を学習した場合には、学習部 1 2 B に登録されている予測モデル 2 0 を、新たに学習した予測モデル 2 0 に更新すればよい。すなわち、学習部 1 2 B には、 1 つの予測モデル 2 0 が格納された状態となる。

# [0071]

図3に戻り説明を続ける。次に、導出部12Cについて説明する。

# [0072]

導出部12Cは、学習部12Bが学習した予測モデル20に基づいて、取得部12Aで取得した動作統計情報42Aからメモリアクセス特性42Bを導出する。導出部12Cがメモリアクセス特性42Bの導出に用いる動作統計情報42Aは、学習部12Bによる予測モデル20の学習時とは異なり、処理回路12が学習用以外の実際のアプリケーション30を実行したときの動作統計情報42Aである。導出部12Cは、この動作統計情報4

10

20

30

40

2 A と、予測モデル 2 0 と、を用いて、メモリアクセス特性 4 2 B を導出する。

## [0073]

図7は、導出部12Cおよび決定部12Dによる処理の一例の説明図である。

#### [0074]

例えば、導出部12 C は、最適化対象のアプリケーション3 2 を処理回路12が実行しているときの動作統計情報42 A を、取得部12 A から取得する。そして、導出部12 C は、取得した動作統計情報42 A を予測モデル2 0 へ入力することで、予測モデル2 0 からの出力として、メモリアクセス特性42 B を得る。

### [0075]

すなわち、導出部12Cは、予測モデル20を用いて、取得部12Aで取得した動作統計情報42Aに対する、メモリアクセス特性42Bの予測値を得る。

## [0076]

決定部12Dは、導出部12Cが導出したメモリアクセス特性42Bに基づいて、アクセス方式を決定する。

#### [0077]

アクセス方式は、処理回路 1 2 による記憶部 1 4 に対するアクセス方式を示す。本実施の形態では、アクセス方式は、第 1 アクセス方式、または、第 2 アクセス方式を示す。

## [0078]

第1アクセス方式は、第2記憶部14Bのデータを第1記憶部14Aへ転送し、該第1記憶部14A内の該データにアクセスする、アクセス方式である。転送およびアクセスするデータは、該アクセス方式の決定に用いた動作統計情報42Aの取得時に処理回路12がアクセスしていたデータである。言い換えると、転送およびアクセスするデータは、該アクセス方式の決定に用いた動作統計情報42Aによって示される動作実行時に処理回路12がアクセスしていたデータである。

### [0079]

本実施の形態では、転送とは、コピーを意味する。上述したように、処理回路12は、ページ単位(第1領域の単位)でデータ転送を行う。また、処理回路12は、キャッシュライン(第2領域)の単位で、記憶部14ヘアクセスする。

# [0080]

このため、第1アクセス方式は、該アクセス方式の決定に用いた動作統計情報42Aによって示される動作実行時に処理回路12がアクセスしていたデータを含むページ(第1領域)内のデータを、第2記憶部14Bから第1記憶部14Aへ転送し、転送後の第1記憶部14Aの該データへアクセスすることを示す。

# [0081]

第2アクセス方式は、第2記憶部14B内のデータにアクセスする方式を示す。本実施の形態では、処理回路12は、原則、第2記憶部14B内のデータにアクセスする。そして、処理回路12は、特定の条件を満たした場合にのみ、第2記憶部14Bから第1記憶部14Aへデータを転送し、第1記憶部14A内のデータへアクセスする。このため、第2アクセス方式は、データを第2記憶部14Bに配置したまま、該第2記憶部14Bにダイレクトにアクセスすることを示す。

### [0082]

例えば、決定部12Dは、導出部12Cが導出したメモリアクセス特性42Bが第1閾値より大きい場合、第2アクセス方式を決定する。また、決定部12Dは、該メモリアクセス特性42Bが第1閾値以下の場合、第1アクセス方式を決定する。

# [0083]

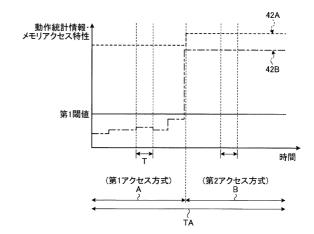

図8は、アクセス方式の決定の説明図である。図8の横軸は時間を示し、縦軸は動作統計情報42Aを示す。

## [0084]

例えば、導出部12Cが、アプリケーション32の実行中に取得部12Aで取得した動作統計情報42Aを予測モデル20へ入力することで、図8に示すメモリアクセス特性4

10

20

30

40

2 Bを導出したと想定する。

### [0085]

なお、動作統計情報 4 2 A が、処理回路 1 2 で実行中のアプリケーションに割当てられた物理メモリサイズを示すと想定する。また、メモリアクセス特性 4 2 B が、アプリケーション 3 2 実行中、単位期間 T あたりに処理回路 1 2 (アプリケーション 3 2 )が使用したメモリサイズを示すと想定する。

## [0086]

この場合、決定部12Dは、導出したメモリアクセス特性42Bが第1閾値より大きい場合、第2アクセス方式を決定する。また、決定部12Dは、導出したメモリアクセス特性42Bが第1閾値以下である場合、第1アクセス方式を決定する。

#### [0087]

図8に示すように、決定部12Dは、アプリケーション32の実行期間TAの内の前半の期間Aのように、メモリアクセス特性42Bが第1閾値以下の場合、第1アクセス方式を決定する。

#### [0088]

すなわち、決定部12Dは、メモリアクセス特性42Bが第1閾値以下である状態を、処理回路12によるメモリアクセスが集中し、アクセスのローカリティの高い状態であると推定する。そして、決定部12Dは、メモリアクセス特性42Bが第1閾値以下の場合、第1アクセス方式を決定する。

# [0089]

このため、決定部12Dは、処理回路12がアクセスのローカリティの高いデータにアクセスする場合、すなわち、記憶部14におけるメモリアクセスされる場所が集中している場合、データを第2記憶部14Bから第1記憶部14Aへ転送し、処理回路12が第1記憶部14A上のデータをキャッシュライン単位でアクセスするように、アクセス方式を決定することができる。

# [0090]

ー方、決定部12Dは、アプリケーション32の実行期間TAの後半の期間Bのように、メモリアクセス特性42Bが第1閾値を超える場合、第2アクセス方式を決定する。

# [0091]

図8に示すように、決定部12Dは、アプリケーション32の実行期間TAの内の後半の期間Bのように、メモリアクセス特性42Bが第1閾値を超える場合、第2アクセス方式を決定する。

# [0092]

すなわち、決定部12Dは、メモリアクセス特性42Bが第1閾値を超える状態を、処理回路12によるメモリアクセスが分散し、アクセスのローカリティが低く、使用中のメモリサイズが大きい状態であると推定する。そして、決定部12Dは、メモリアクセス特性42Bが第1閾値を超える場合、第2アクセス方式を決定する。

# [0093]

[0094]

メモリアクセス特性42Bが第1閾値を超える場合、第2アクセス方式を決定することで、決定部12Dは、処理回路12によるメモリアクセスの高速化を図ることができる。

ここで、メモリアクセス特性 4 2 B が第 1 閾値を超える場合には、第 2 記憶部 1 4 B のデータを第 1 記憶部 1 4 A へ転送しても、第 1 記憶部 1 4 A の空き容量不足により、すぐに第 1 記憶部 1 4 A から第 2 記憶部 1 4 B へデータが転送されてしまう。すなわち、メモリアクセス特性 4 2 B が第 1 閾値を超える場合に、第 2 記憶部 1 4 B のデータを第 1 記憶部 1 4 A へ転送すると、第 1 記憶部 1 4 A と第 2 記憶部 1 4 B との間のページ単位のデータ入れ替えが頻発してしまい、処理回路 1 2 の性能低下を引き起こす可能性がある。

## [0095]

そこで、本実施の形態では、決定部12Dは、メモリアクセス特性42Bが第1閾値を 超える場合には、第2アクセス方式を決定する。このため、決定部12Dは、処理回路1 10

20

30

40

2によるメモリアクセスの高速化を図ることができる。

## [0096]

なお、第1閾値には、任意の値を予め定めればよい。例えば、第1閾値には、処理回路 12が利用可能な、第1記憶部14Aのサイズやこれに近い値であればよい。

# [0097]

処理回路 1 2 が利用可能なサイズとは、具体的には、処理回路 1 2 が実行するアプリケーション 3 2 で利用可能な、第 1 記憶部 1 4 A のサイズや、情報処理装置 1 0 で利用可能な記憶部 1 4 のサイズなどである。なお、第 1 閾値は、これらの利用可能なサイズに対して所定の割合大きい値であってもよい。また、第 1 閾値は、これらの利用可能なサイズに対して所定の割合小さい値であってもよい。

## [0098]

なお、第1閾値を、処理回路12が実行するアプリケーション32で利用可能な第1記憶部14Aのサイズより大きい値、または、情報処理装置10で利用可能な第1記憶部14Aのサイズより大きい値とすると、以下の効果が得られる。例えば、第1記憶部はは高速なSCMを想定しているため、第1アクセス方式が決定された場合における、第1記憶部14Aと第2記憶部14Bとの間のデータの転送は、高速に行う事が可能である。第1記憶部14Bから第1記憶部14Aへのデータ転送あるいは第1記憶部14Aのがデータ転送を積極的に行って頻繁にデータを入れ替えても速度低低値で済み高速に処理することができる。このため、利用可能な第1記憶部14Aのサイズより大きい値とすることで、利用可能な第1記憶部14Aを最大限活用して、より大きなメモリサイズを利用するアプリケーションが実行可能になる。また、利用可能な第1記憶部14Aのサイズよりサイズを利用するアプリケーションが実行可能になる。また、利用可能な第1記憶部14Aのサイズは、第1閾値を、利用可能な第1記憶部14Aのサイズより小さいサイズで、きい値とすることで、実際に利用可能な第1記憶部14Aのサイズより小さいサイズで、使用メモリサイズが小さく(つまり消費電力が低く)速度低下も抑えた効率の良い処理を実行することができる。

## [0099]

図3に戻り説明を続ける。次に、実行部12Eについて説明する。実行部12Eは、決定部12Dで決定されたアクセス方式に応じて、データの第2記憶部14Bから第1記憶部14Aへの転送および第1記憶部14A内の該データへのアクセス、または、第2記憶部14B内のデータへのアクセス、を実行する。

# [0100]

すなわち、決定部12Dが第1アクセス方式を決定した場合、実行部12Eは、該アクセス方式の決定に用いた動作統計情報42Aによって示される動作実行時に処理回路12がアクセスしていたデータを含むページ(第1領域)を、第2記憶部14Bから第1記憶部14Aへ転送し、第1記憶部14Aにおける転送した該ページ内の該データへのアクセスを実行する。

# [0101]

なお、実行部12Eによる、第1記憶部14Aから第2記憶部14Bへのデータ転送のタイミングは、限定されない。例えば、実行部12Eは、決定部12Dが第1アクセス方式を決定した直後、実行部12Eが次回該データへアクセスする時、予め定めた条件を満たしたタイミング、の何れであってもよい。予め定めた条件を満たすタイミングは、例えば、処理回路12による記憶部14へのメモリアクセスが所定値以下の期間などである。

## [0102]

一方、決定部12Dが第2アクセス方式を決定した場合、実行部12Eは、該アクセス方式の決定に用いた動作統計情報42Aによって示される動作実行時に処理回路12がアクセスしていた、第2記憶部14B内のデータへのアクセスを継続して実行する。

## [0103]

次に、変更部12Fについて説明する。決定部12Dが第1アクセス方式を決定した場合、変更部12Fは、第1記憶部14Aの、利用可能なメモリサイズを変更する。

10

20

30

40

# [0104]

詳細には、変更部12Fは、第1記憶部14Aの利用可能なメモリサイズを、第1アクセス方式の決定に用いたメモリアクセス特性42Bによって示される、処理回路12がアプリケーション32の実行中に単位期間Tあたりに使用したメモリサイズに変更する。また、変更部12Fは、第1記憶部14Aの利用可能なメモリサイズを、該使用した該メモリサイズより一定の割合大きいサイズ、または、該使用した該メモリサイズより一定の割合小さいサイズに変更する。そして、変更部12Fは、利用可能なメモリサイズを変更した後の第1記憶部14Aにおける、利用不可能な領域を、パワーオフまたはセルフリフレッシュモードなどの低消費電力モードに設定すればよい。

#### [ 0 1 0 5 ]

なお、処理回路12は、変更部12Fを備えない構成であってもよい。すなわち、処理 回路12は、第1記憶部14Aにおける利用可能なメモリサイズの変更を行わない形態で あってもよい。

## [0106]

次に、本実施の形態の処理回路12が実行する情報処理の手順の一例を説明する。

#### [ 0 1 0 7 ]

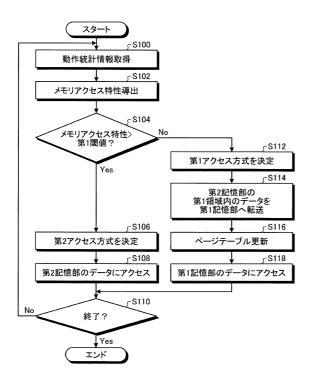

図9は、本実施の形態の処理回路12が実行する情報処理の手順の一例を示す、フローチャートである。なお、図9に示す情報処理の手順の実行前に、学習部12Bが、予測モデル20を学習済であるものとして説明する。また、図9には、変更部12Fが第1記憶部14Aの利用可能なメモリサイズの変更処理を実行しない形態を、一例として示した。

[0108]

まず、取得部12Aが、単位期間Tにおける、処理回路12の動作統計情報42Aを取得する(ステップS100)。

#### [0109]

次に、導出部12Cが、学習部12Bが学習した予測モデル20に、ステップS100で取得した動作統計情報42Aを入力することで、メモリアクセス特性42Bを導出する(ステップS102)。

# [0110]

次に、決定部12Dが、ステップS102で導出したメモリアクセス特性42Bが第1 閾値より大きいか否かを判断する(ステップS104)。

# [0111]

メモリアクセス特性 4 2 B が第 1 閾値より大きいと判断した場合(ステップ S 1 0 4 : Y e s )、ステップ S 1 0 6 へ進む。

## [0112]

ステップS106では、決定部12Dは、第2アクセス方式を決定する(ステップS1 06)。次に、実行部12Eは、ステップS100で取得した動作統計情報42Aを示す 処理を実行中の処理回路12がアクセス中の、第2記憶部14Bのデータを、該第2記憶 部14Bに配置したまま、該第2記憶部14Bにアクセスする(ステップS108)。

# [0113]

次に、処理回路12は、情報処理を終了するか否かを判断する(ステップS110)。例えば、処理回路12は、ステップS100で取得した動作統計情報42Aを示す処理を実行中のアプリケーション32の終了指示を受付けたか否かを判別することで、ステップS110の判断を行う。ステップS110で肯定判断すると(ステップS110:Yes)、本ルーチンを終了する。一方、ステップS110で否定判断すると(ステップS110:No)、上記ステップS100へ戻る。

### [0114]

一方、上記ステップS104で、ステップS102で導出したメモリアクセス特性42 Bが第1閾値以下であると判断すると(ステップS104:No)、ステップS112へ 進む。

# [0115]

10

20

30

40

ステップS112では、決定部12Dは、第1アクセス方式を決定する(ステップPS 112)。次に、実行部12Eは、ステップS100で取得した動作統計情報42Aによって示される動作実行時に処理回路12がアクセスしていた、第2記憶部14Bの第1領域内(ページ内)のデータを、該第2記憶部14Bから第1記憶部14Aへ転送する(ステップS114)。

## [0116]

次に、実行部12Eは、ページテーブルにおける、ステップS114で転送した第1領域の論理アドレスに対応する物理アドレスを、ステップS114で転送した転送先の第1記憶部14Aの格納先を示す物理アドレスに更新する(ステップS116)。このため、処理回路12は、該データにアクセスする場合には、第1記憶部14Aにアクセスすることで、該データにアクセスすることが可能となる。

## [0117]

そして、実行部12Eは、ステップS114で第1記憶部14Aへ転送されたデータに アクセスする(ステップS118)。そして、上記ステップS110へ進む。

#### [0118]

以上説明したように、本実施の形態の情報処理装置10は、取得部12Aと、導出部12Cと、決定部12Dと、を備える。取得部12Aは、処理回路12の動作統計情報42Aを取得する。導出部12Cは、動作統計情報42Aから処理回路12のメモリアクセス特性42Bを導出するための予測モデル20に基づいて、取得した動作統計情報42Aからメモリアクセス特性42Bを導出する。決定部12Dは、導出したメモリアクセス特性42Bに基づいて、第1記憶部14Aより処理回路12によるアクセス速度が遅い第2記憶部14Bのデータを第1記憶部14Aへ転送し、第1記憶部14A内の該データにアクセスする第1アクセス方式、または、第2記憶部14B内のデータにアクセスする第2アクセス方式、の何れかのアクセス方式を決定する。

### [0119]

このように、本実施の形態の情報処理装置10は、予測モデル20に基づいて、第1アクセス方式または第1アクセス方式の何れかのアクセス方式を決定する。

# [0120]

ここで、従来では、複数種類のメモリ(記憶部 1 4 )の使い分けに用いる情報を効率よく提供することは困難であった。

# [0121]

SCMなどの第2記憶部14Bは、DRAMなどの第1記憶部14Aより大容量であるがアクセス速度が遅い。このため、処理対象のデータの特性に合わせて、データを第1記憶部14Aと第2記憶部14Bとに分散して格納してアクセスすると、処理回路12は効率よくデータ処理を実行することができる。すなわち、処理回路12によるアクセスのローカリティが低く、メモリアクセスされる場所が広域に分散されることでアクセスするデータサイズが大きい場合には、データを第2記憶部14Bに配置したままとし、処理回路12が第2記憶部14Bにダイレクトにアクセスすることが好ましい。また、メモリアクセスされる場所が集中することで、アクセスのローカリティの高いデータに処理回路12がアクセスする場合には、データを第2記憶部14Bから第1記憶部14Aへ転送(コピー)し、処理回路12は第1記憶部14A上のデータをキャッシュライン単位でアクセスすることが好ましい。

# [0122]

しかし、従来では、複数種類の記憶部14の使い分けに用いる情報、すなわち、処理回路12のメモリアクセス特性42Bを、効率よく得ることが困難であった。

#### [0123]

一方、本実施の形態の情報処理装置10では、予測モデル20に基づいて、取得した動作統計情報42Aからメモリアクセス特性42Bを導出し、第1アクセス方式または第1アクセス方式の何れかのアクセス方式を決定する。

# [0124]

10

20

30

従って、本実施の形態の情報処理装置10は、複数種類のメモリの使い分けに用いる情報を効率よく提供することができる。

#### [0125]

## (変形例1)

なお、上記実施の形態では、情報処理の手順の説明時に、変更部 1 2 F が変更処理を実行しない形態を、一例として示した。

# [0126]

しかし、情報処理の手順の実行時に、変更部12Fによる変更処理を実行してもよい。

# [0127]

この場合、例えば、図9に示すステップS112の第アクセス方式を決定した後に、変更部12Fが、第1記憶部14Aの利用可能なメモリサイズを変更する変更処理を実行すればよい。そして、その次に、上記ステップS114~ステップS118の処理を実行すればよい。

## [0128]

なお、変更部12Fによる変更処理のタイミングは、このタイミングに限定されない。例えば、変更部12Fは、第1アクセス方式が決定され、第2記憶部14Bの第1領域内のデータが第1記憶部14Aへ転送された後に、変更処理を実行してもよい。また、変更部12Fは、第1アクセス方式が決定され、第2記憶部14Bの第1領域内のデータが第1記憶部14Aへ転送され、更に、実行部12Eが第1記憶部14Aのデータにアクセスした後に、変更処理を実行してもよい。

## [0129]

# (変形例2)

なお、上記実施の形態では、決定部12Dは、導出部12Cが導出したメモリアクセス特性42Bが第1閾値より大きい場合、第2アクセス方式を決定する形態を説明した。また、決定部12Dは、該メモリアクセス特性42Bが第1閾値以下の場合、第1アクセス方式を決定する形態を説明した。

## [0130]

しかし、決定部12Dは、他の方法により、第1アクセス方式または第2アクセス方式 を決定してもよい。

## [0131]

例えば、決定部12Dは、メモリアクセス特性42Bの比率が、第2閾値より大きい場合、第2アクセス方式を決定する。メモリアクセス特性42Bの比率とは、取得部12Aが取得した動作統計情報42Aによって示される動作実行時に実行中の、1または複数のアプリケーション32の各々に割当てられた、物理メモリサイズの合計値に対する、メモリアクセス特性42Bの比率(割合)を示す。

# [0132]

具体的には、決定部12Dは、実行中のアプリケーション32の各々に割当てられた物理メモリサイズの合計値に対する、導出部12Cで導出されたメモリアクセス特性42Bとしての使用中のメモリサイズの比率が、第2閾値以下の場合、第1アクセス方式を決定する。

### [0133]

該比率が第2閾値以下の状態とは、アプリケーション32で利用する可能性のあるメモリの一部の領域に対して、メモリアクセスが集中している状態を示す。このため、この場合、決定部12Dは、処理回路12がアクセスのローカリティの高いデータにアクセスしていると判断し、第2記憶部14B上のデータをページ単位(第1領域単位)で第1記憶部14Aへ転送し、アクセスする第1アクセス方式を決定する。

#### [0134]

一方、決定部12Dは、該比率が第2閾値を超える場合、第2アクセス方式を決定する

[0135]

10

20

30

20

30

40

50

該比率が第2閾値を超える状態とは、アプリケーション32で利用する可能性のあるメモリ領域全体に対する処理回路12によるアクセスが、該メモリ領域全体に分散されている状況であることを示す。このため、該比率が第2閾値を超える状態の場合、アクセスのローカリティが低く、使用中のメモリサイズが大きい状態である。このため、この場合、決定部12Dは、第2アクセス方式を決定する。

# [0136]

なお、第2閾値は、予め任意の値を定めればよい。例えば、第2閾値は、上記1または複数のアプリケーション32の各々に割当てられた物理メモリサイズの合計値のN分の1(Nは、2以上の整数)。例えば、第2閾値は、上記合計値の1/3、1/5、1/7、1/10などの値などである。基本的な考え方としては、利用するDRAMに対してそれに見合う高速化が得られる場合は第1アクセス方式を選択したい。あるアプリケーションに対して、そのアプリケーションに割り当てられた物理メモリサイズを10としたときに、DRAMを1あるいは2あるいは3程度利用することでDRAM利用による消費電力増加やコストを抑えつつDRAM利用による局所性の高い処理の高速化が得られるのが好ましいためである。

#### [0137]

次に、決定部12Dが比率を用いてアクセス方式を決定する場合に、処理回路12が実行する情報処理の手順の一例を説明する。

## [0138]

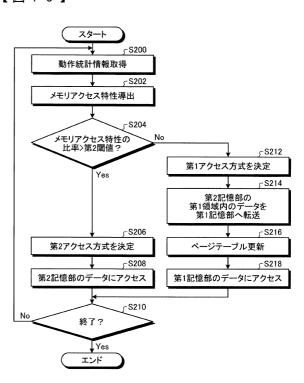

図 1 0 は、本変形例の処理回路 1 2 が実行する情報処理の手順の一例を示す、フローチャートである。

#### [0139]

まず、処理回路12は、上記実施の形態のステップS100~ステップS102(図9 参照)と同様にして、ステップS200~ステップS202の処理を実行する。

#### [0140]

詳細には、取得部12Aが、単位期間Tにおける、処理回路12の動作統計情報42Aを取得する(ステップS200)。次に、導出部12Cが、学習部12Bが学習した予測モデル20に、ステップS200で取得した動作統計情報42Aを入力することで、メモリアクセス特性42Bを導出する(ステップS202)。

#### [0141]

次に、決定部 1 2 Dが、ステップ S 2 0 2 で導出したメモリアクセス特性 4 2 B の比率が、第 2 閾値より大きいか否かを判断する(ステップ S 2 0 4 )。

# [0142]

メモリアクセス特性 4 2 B の比率が第 2 閾値より大きいと判断した場合(ステップ S 2 0 4 : Y e s )、上記実施の形態のステップ S 1 0 6 ~ ステップ S 1 1 0 (図 9 参照)と同様にして、ステップ S 2 0 6 ~ ステップ S 2 0 8 ~ ステップ S 2 1 0 の処理を実行する

# [0143]

一方、メモリアクセス特性 4 2 B の比率が第 2 閾値以下と判断した場合(ステップ S 2 0 4 : N o )、上記実施の形態のステップ S 1 1 2 ~ ステップ S 1 1 8 (図 9 参照)と同様にして、ステップ S 2 1 2 ~ ステップ S 2 1 8 の処理を実行する。そして、ステップ S 2 1 0 で肯定判断すると(ステップ S 2 1 0 : Y e s )、本ルーチンを終了する。

# [0144]

以上説明したように、決定部12Dは、導出部12Cで導出したメモリアクセス特性4 2Bの比率が、第2閾値より大きいか否かを判断することで、アクセス方式を決定しても よい。この場合についても、上記実施の形態と同様の効果が得られる。

# [0145]

なお、上記実施の形態および変形例では、情報処理装置10が、処理回路12と、キャッシュメモリ16と、管理装置18と、を備える形態を一例として説明した(図1参照)。しかし、情報処理装置10は、処理回路12と、キャッシュメモリ16と、管理装置1

8と、記憶部14と、を備えた構成であってもよい。また、処理回路12が、キャッシュメモリ16および管理装置18の少なくとも一方を含む構成であってもよい。また、管理装置18が、記憶部14およびキャッシュメモリ16を備えた構成であってもよい。

#### [0146]

以上、本発明の実施の形態および変形例を説明したが、これらの実施の形態および変形例は、例として提示したものであり、発明の範囲を限定することは意図していない。これら新規な実施の形態および変形例は、その他の様々な形態で実施されることが可能であり、発明の要旨を逸脱しない範囲で、種々の省略、置き換え、変更を行うことができる。これらの実施の形態やその変形例は、発明の範囲や要旨に含まれるとともに、請求の範囲に記載された発明とその均等の範囲に含まれる。

# 【符号の説明】

# [0147]

- 10 情報処理装置

- 12 処理回路

- 1 2 A 取得部

- 1 2 B 学習部

- 1 2 C 導出部

- 1 2 D 決定部

- 1 2 E 実行部

- 1 2 F 変更部

- 1 4 記憶部

- 1 4 A 第 1 記憶部

- 1 4 B 第 2 記憶部

- 20 予測モデル

# 【図1】

# 【図2】

10

【図3】

【図4】

【図5】

【図6A】

【図 6 B】

【図7】

(予測モデル

【図8】

【図9】

【図10】