## (19) **日本国特許庁(JP)**

# (12) 公 開 特 許 公 報(A)

(11)特許出願公開番号

特開2013-122939 (P2013-122939A)

(43) 公開日 平成25年6月20日(2013.6.20)

(51) Int.Cl.

FΙ

テーマコード (参考)

HO5K 3/34

(2006.01)

H05K 501Z 3/34 501D HO5K 3/34

5E319

審査請求 未請求 請求項の数 5 OL (全 10 頁)

(21) 出願番号 (22) 出願日

特願2011-269809 (P2011-269809)

平成23年12月9日 (2011.12.9)

(71) 出願人 000002185

ソニー株式会社

東京都港区港南1丁目7番1号

(74)代理人 100116942

弁理士 岩田 雅信

(72) 発明者 竹田 幸広

東京都港区港南1丁目7番1号 ソニーイ

ーエムシーエス株式会社内

(72) 発明者 前田 篤史

東京都港区港南1丁目7番1号 ソニーイ

ーエムシーエス株式会社内

Fターム(参考) 5E319 AA03 AC02 AC11 AC20 BB05

CC33 CD26 GG03 GG20

### (54) 【発明の名称】回路基板

### (57)【要約】

【課題】 製造コストの高騰及び設計の自由度の低下を 来たすことなく鳴きの発生を抑制する。

【解決手段】 複数の誘電体層と複数の内部電極とが交 互に積層された素体の両端部に内部電極が接続された一 対の外部電極が設けられた積層セラミックコンデンサー と、絶縁基板と絶縁基板上に銅箔によって形成され積層 セラミックコンデンサーの一対の外部電極がそれぞれ接 続される一対のランドとを有する配線板とを設け、配線 板における一対のランド間に積層セラミックコンデンサ の素体と配線板の接触を抑制する接触抑制部を設けた

これにより接触抑制部によって積層セラミックコンデ ンサーの素体と配線板の間に隙間が形成され、製造コス トの高騰及び設計の自由度の低下を来たすことなく鳴き の発生を抑制することができる。

【選択図】 図 1 2…配線板 3…積層セラミックコンデンサ

5a…ランド 6…シルク印刷部

7---素体 8…外部電極

#### 【特許請求の範囲】

### 【請求項1】

複数の誘電体層と複数の内部電極とが交互に積層された素体の両端部に前記内部電極が接続された一対の外部電極が設けられた積層セラミックコンデンサーと、

絶縁基板と前記絶縁基板上に銅箔によって形成され前記積層セラミックコンデンサーの 一対の外部電極がそれぞれ接続される一対のランドとを有する配線板とを備え、

前記配線板における前記一対のランド間に前記積層セラミックコンデンサーの素体と前記配線板の接触を抑制する接触抑制部を設けた

回路基板。

### 【請求項2】

前記接触抑制部として、前記絶縁基板上にシルク印刷部を設けた 請求項1に記載の回路基板。

### 【請求項3】

前記シルク印刷部を前記一対のランドの並び方向に離隔して二つ設けた 請求項2に記載の回路基板。

### 【請求項4】

前記接触抑制部として、前記積層セラミックコンデンサーの素体と前記絶縁基板の間の前 記銅箔をエッチングによって除去することにより離隔空間を形成した

請求項1に記載の回路基板。

### 【請求項5】

前記接触抑制部として、前記絶縁基板上に設けたシルク印刷部と、前記積層セラミックコンデンサーの素体と前記絶縁基板の間の前記銅箔をエッチングによって除去することにより離隔空間とを形成した

請求項1に記載の回路基板。

【発明の詳細な説明】

### 【技術分野】

### [0001]

本技術は回路基板についての技術分野に関する。詳しくは、配線板における一対のランド間に積層セラミックコンデンサーの素体と配線板の接触を抑制する接触抑制部を設けて製造コストの高騰及び設計の自由度の低下を来たすことなく鳴きの発生を抑制する技術分野に関する。

#### 【背景技術】

### [0002]

テレビジョン受像器やパーソナルコンピューターや音響機器等の各種の電子機器には、 内部に回路基板が配置されている。回路基板には、例えば、絶縁基板上に銅箔によって回 路パターンが形成された配線板と配線板の回路パターン上に実装された複数の電子部品と を有しているものがある。

### [0003]

このような回路基板には電子部品として積層セラミックコンデンサーが設けられたものがある。積層セラミックコンデンサーは複数の誘電体層と複数の内部電極とが交互に積層された素体の両端部に内部電極が接続された一対の外部電極が設けられ、一対の外部電極が回路パターンの一対のランドに半田等によって接続される。

## [0004]

積層セラミックコンデンサーは所定の大きさの電圧が印加されることにより動作されるが、積層セラミックコンデンサーに電圧が印加されると、電圧の印加に伴う電歪効果により誘電体に機械的な歪みが発生して振動し、この振動が配線板に伝達されて可聴域の音に変換され所謂鳴きが発生することが知られている。

### [00005]

鳴きの発生は電子機器の使用者に違和感を与えると共に不快感を感じさせ、特に、音響機器においてはノイズになってしまう場合がある。

10

20

30

40

#### [0006]

従来の回路基板には、上記した鳴きの発生を抑制するための各種の手段が講じられたものがある(例えば、特許文献1乃至特許文献10参照)。

#### [0007]

特許文献 1 に記載された回路基板にあっては、鳴きの発生を抑制するために、積層セラミックコンデンサーを配線板の表面から浮かすために L 字状の金属端子を積層セラミックコンデンサーの両端部に接合している。

### [00008]

特許文献 2 に記載された回路基板にあっては、鳴きの発生を抑制するために、配線板と 積層セラミックコンデンサーの間に絶縁基板を挿入している。

#### [0009]

特許文献 3 乃至特許文献 6 に記載された回路基板にあっては、鳴きの発生を抑制するために、積層セラミックコンデンサーの層構造を変更している。

### [0010]

特許文献 7 に記載された回路基板にあっては、鳴きの発生を抑制するために、外部電極に突起部を設け突起部を L 字状の金具に半田付けしている。

#### [0011]

特許文献 8 に記載された回路基板にあっては、鳴きの発生を抑制するために、積層セラミックコンデンサーの中央部に突部を設け積層セラミックコンデンサーと配線板の間に隙間を形成している。

### [0012]

特許文献 9 に記載された回路基板にあっては、鳴きの発生を抑制するために、複数の積層セラミックコンデンサーを鳴きをキャンセルするように配置している。

#### [0013]

特許文献10に記載された回路基板にあっては、鳴きの発生を抑制するために、内部電極が配線板の実装面に対して平行になるように積層セラミックコンデンサーを実装している。

### [0014]

【 特 許 文 献 1 】 特 開 2 0 1 0 - 1 8 6 8 8 4 号 公 報

【特許文献 2 】特開 2 0 1 0 - 1 6 1 1 7 2 号公報

【特許文献3】特開2009-71106号公報

【特許文献 4 】特開 2 0 0 9 - 2 7 1 0 1 号公報

【特許文献 5 】特開 2 0 0 6 - 1 9 9 5 6 3 号公報

【特許文献 6 】特開 2 0 0 7 - 5 3 0 9 2 5 号公報

【特許文献7】特開2000-235931号公報

【特許文献8】特開平11-40456号公報

【特許文献9】特開2002-232110号公報

【特許文献10】特開2011-108827号公報

### 【発明の開示】

【発明が解決しようとする課題】

#### [0015]

ところが、特許文献 1 乃至特許文献 8 に記載された回路基板にあっては、積層セラミックコンデンサーの加工や構造の変更が必要であり、材料費や加工費が高くなり製造コストが高騰すると言う問題がある。

## [0016]

また、特許文献 9 及び特許文献 1 0 に記載された回路基板にあっては、積層セラミックコンデンサーの配線板に対する実装位置が制限され、回路基板の設計の自由度が低下すると言う問題がある。

## [0017]

そこで、本技術回路基板は、上記した問題点を克服し、製造コストの高騰及び設計の自

10

20

30

40

由度の低下を来たすことなく鳴きの発生を抑制することを課題とする。

### 【課題を解決するための手段】

#### [0018]

第1に、回路基板は、上記した課題を解決するために、複数の誘電体層と複数の内部電極とが交互に積層された素体の両端部に前記内部電極が接続された一対の外部電極が設けられた積層セラミックコンデンサーと、絶縁基板と前記絶縁基板上に銅箔によって形成され前記積層セラミックコンデンサーの一対の外部電極がそれぞれ接続される一対のランドとを有する配線板とを備え、前記配線板における前記一対のランド間に前記積層セラミックコンデンサーの素体と前記配線板の接触を抑制する接触抑制部を設けたものである。

#### [0019]

従って、回路基板にあっては、接触抑制部によって積層セラミックコンデンサーの素体と配線板の間に隙間が形成される。

### [0020]

第2に、上記した回路基板においては、前記接触抑制部として、前記絶縁基板上にシルク印刷部を設けることが望ましい。

#### [0021]

接触抑制部として、絶縁基板上にシルク印刷部を設けることにより、回路基板に対する各種の表示等を目的とした同じ製造工程においてシルク印刷部を設けることが可能になる

## [0022]

第3に、上記した回路基板においては、前記シルク印刷部を前記一対のランドの並び方向に離隔して二つ設けることが望ましい。

## [0023]

シルク印刷部を一対のランドの並び方向に離隔して二つ設けることにより、二つのシルク印刷部に載置された状態で積層セラミックコンデンサーの一対の外部電極が一対のランドに接合される。

### [0024]

第4に、上記した回路基板においては、前記接触抑制部として、前記積層セラミックコンデンサーの素体と前記絶縁基板の間の前記銅箔をエッチングによって除去することにより離隔空間を形成することが望ましい。

### [0025]

接触抑制部として、積層セラミックコンデンサーの素体と絶縁基板の間の銅箔をエッチングによって除去することにより離隔空間を形成することにより、離隔空間によって積層セラミックコンデンサーと配線板の接触が抑制される。

### [0026]

第5に、上記した回路基板においては、前記接触抑制部として、前記絶縁基板上に設けたシルク印刷部と、前記積層セラミックコンデンサーの素体と前記絶縁基板の間の前記銅箔をエッチングによって除去することにより離隔空間とを形成することが望ましい。

### [0027]

接触抑制部として、絶縁基板上に設けたシルク印刷部と、積層セラミックコンデンサーの素体と絶縁基板の間の銅箔をエッチングによって除去することにより離隔空間とを形成することにより、シルク印刷部と離隔空間によって積層セラミックコンデンサーと配線板の接触が抑制される。

### 【発明の効果】

### [0028]

本技術回路基板は、複数の誘電体層と複数の内部電極とが交互に積層された素体の両端部に前記内部電極が接続された一対の外部電極が設けられた積層セラミックコンデンサーと、絶縁基板と前記絶縁基板上に銅箔によって形成され前記積層セラミックコンデンサーの一対の外部電極がそれぞれ接続される一対のランドとを有する配線板とを備え、前記配線板における前記一対のランド間に前記積層セラミックコンデンサーの素体と前記配線板

10

20

30

40

の接触を抑制する接触抑制部を設けている。

### [0029]

従って、積層セラミックコンデンサーの加工や構造の変更を必要とせず積層セラミックコンデンサーの配線板に対する実装位置も制約されないため、製造コストの高騰及び設計の自由度の低下を来たすことなく鳴きの発生を抑制することができる。

#### [0030]

請求項2に記載した技術にあっては、前記接触抑制部として、前記絶縁基板上にシルク印刷部を設けている。

### [0031]

従って、回路基板に対する各種の表示等を目的とした同じ製造工程においてシルク印刷部を設けることができ、製造工程の追加を必要とせず、その分、製造コストの高騰や製造時間の増大を来たすことなく鳴きの発生を抑制することができる。

### [0032]

請求項3に記載した技術にあっては、前記シルク印刷部を前記一対のランドの並び方向に離隔して二つ設けている。

#### [0033]

従って、積層セラミックコンデンサーを配線板に対して安定した状態で実装することができる。

### [0034]

請求項4に記載した技術にあっては、前記接触抑制部として、前記積層セラミックコンデンサーの素体と前記絶縁基板の間の前記銅箔をエッチングによって除去することにより離隔空間を形成している。

### [0035]

従って、製造コストの高騰及び設計の自由度の低下を来たすことなく鳴きの発生を抑制 することができる。

## [0036]

請求項5に記載した技術にあっては、前記接触抑制部として、前記絶縁基板上に設けた シルク印刷部と、前記積層セラミックコンデンサーの素体と前記絶縁基板の間の前記銅箔 をエッチングによって除去することにより離隔空間とを形成している。

### [0037]

従って、製造コストの高騰及び設計の自由度の低下を来たすことなく鳴きの発生を抑制 することができる。

【発明を実施するための最良の形態】

### [0038]

以下に、本技術回路基板を実施するための最良の形態を添付図面に従って説明する。

## [0039]

### 「回路基板の構成]

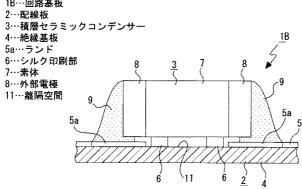

回路基板1は、配線板(実装基板)2と配線板2上に実装された積層セラミックコンデンサー3とを有している(図1参照)。

### [0040]

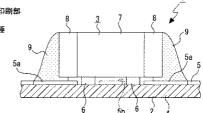

配線板 2 は絶縁基板 4 上に所定の回路パターン 5 が形成され、回路パターン 5 には積層セラミックコンデンサー 3 が接合される一対のランド 5 a、 5 a が形成されている(図 1 及び図 2 参照)。回路パターン 5 は厚さが 2 0  $\mu$  m ~ 3 0  $\mu$  m 程度の銅箔によって形成されている。ランド 5 a、 5 a は、例えば、長方形状に形成され、並び方向に直交する方向が長手方向にされている。

#### [0041]

絶縁基板4としては、例えば、ガラスエポキシ基板、紙フェノール基板、紙エポキシ基板、ガラスコンポジット基板等が用いられている。

## [0042]

配線板2にはランド5a、5aの間にシルクスクリーン印刷によって形成された二つの

10

20

30

40

シルク印刷部6、6が設けられている。

### [0043]

シルク印刷部 6 、 6 は厚みがランド 5 a 、 5 a の厚みより厚くされており、例えば、 3 0  $\mu$  m ~ 5 0  $\mu$  m にされている。シルク印刷部 6 、 6 はそれぞれランド 5 a 、 5 a の内側の近傍に位置され、ランド 5 a 、 5 a の長手方向にに延びる形状に形成されている。シルク印刷部 6 、 6 の幅は、例えば、 0 . 3 m m 程度にされ、長さがランド 5 a 、 5 a と同じか稍長く形成されている。

### [0044]

シルクスクリーン印刷は回路基板に対して、例えば、製造者の略号、部品番号、部品名、ヒューズの定格の表示、回路の境界の表示等を目的として製造工程の一つとして行われる。従って、シルクスクリーン印刷によるシルク印刷部6、6の形成も、これらの表示等を目的とした同じ製造工程において行うことができる。

#### [0045]

積層セラミックコンデンサー3は図示しない複数の誘電体層と図示しない複数の内部電極とが交互に積層された素体7の両端部に内部電極が接続された一対の外部電極8、8が設けられて成る(図1参照)。

### [0046]

積層セラミックコンデンサー3は素体7の外部電極8、8側の端部がそれぞれシルク印刷部6、6に載置された状態において、外部電極8、8がそれぞれランド5a、5aに半田9、9によって接合される。

### [0047]

このように積層セラミックコンデンサー3がシルク印刷部6、6に載置された状態でランド5a、5aに接合されることにより、積層セラミックコンデンサー3の素体7と絶縁基板4の間に一定の隙間が形成される。

#### [0048]

積層セラミックコンデンサー3に電圧が印加されると、電圧の印加に伴う電歪効果により誘電体に機械的な歪みが発生して振動するが、シルク印刷部6、6によって素体7と絶縁基板4の間に一定の隙間が形成されているため、積層セラミックコンデンサー3に振動が生じても素体7が絶縁基板4(配線板2)に接触し難い状態にされている。従って、シルク印刷部6、6は、積層セラミックコンデンサー3に電圧の印加に伴う電歪効果が生じたときに、素体7と配線板2の接触を抑制する接触抑制部として機能し、接触抑制部によって可聴域の音が出力される鳴きの発生が抑制される。

### [0049]

#### 「まとめ ]

以上に記載した通り、回路基板1にあっては、積層セラミックコンデンサー3に電圧の印加に伴う電歪効果が生じたときに素体7と配線板2の接触を抑制する接触抑制部としてシルク印刷部6、6が設けられている。

## [0050]

従って、積層セラミックコンデンサー3の加工や構造の変更を必要とせず積層セラミックコンデンサー3の配線板2に対する実装位置も制約されないため、製造コストの高騰及び設計の自由度の低下を来たすことなく鳴きの発生を抑制することができる。

### [0051]

特に、シルク印刷部6、6を設けるためのシルクスクリーン印刷は、上記したように、 回路基板1に対する各種の表示等を目的とした同じ製造工程において行うことができ、製 造工程の追加を必要とせず、その分、製造コストの高騰や製造時間の増大を来たすことな く鳴きの発生を抑制することができる。

### [0052]

接触抑制部としてシルク印刷部6、6を設ける構成は、図1に示すように、素体7と絶縁基板4の間に回路パターン5の一部5bが形成されている場合に特に有効である。

### [0053]

40

30

10

20

尚、上記には、二つのシルク印刷部6、6を設けた例を示したが、シルク印刷部6の数は任意であり、例えば、ランド5a、5aの中央部に一つのシルク印刷部6が設けられていてもよく、また、ランド5a、5aの中央部に三つ以上のシルク印刷部6、6、・・・が設けられていてもよい。

#### [0054]

但し、ランド5a、5a間に二つのシルク印刷部6、6が設けられることにより、積層セラミックコンデンサー3を配線板2に対して安定した状態で実装することができる。

#### [0055]

### 「測定値 ]

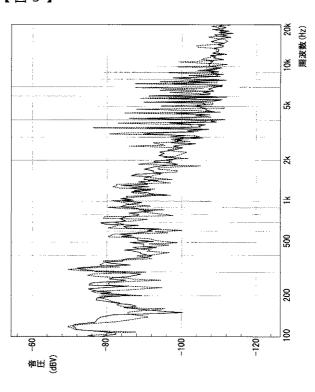

以下に、シルク印刷部6、6が設けられた回路基板1とシルク印刷部6、6が設けられていない回路基板について比較した測定値について説明する(図3参照)。

#### [0056]

図3は、可聴範囲とされる周波数領域に対する音圧レベルを測定した値を示し、実線はシルク印刷部6、6が設けられた回路基板1についての測定値を示し、破線はシルク印刷部6、6が設けられていない回路基板についての測定値を示す。横軸は周波数であり、縦軸は音圧レベルである。

### [0057]

図3に示すように、シルク印刷部6、6が設けられた回路基板1の音圧レベルはシルク印刷部6、6が設けられていない回路基板の音圧レベルに対して低下されており、特に、2KHz以上の高周波領域における音圧レベルが低下されている。

### [0058]

このようにシルク印刷部6、6が設けられた回路基板1の音圧レベルはシルク印刷部6、6が設けられていない回路基板の音圧レベルに対して低下されており、可聴域の音が出力される鳴きの発生が抑制されていることが実証された。

#### [0059]

## [変形例]

以下に、鳴きの発生を抑制する回路基板の各変形例について説明する(図 4 及び図 5 参照)。

### [0060]

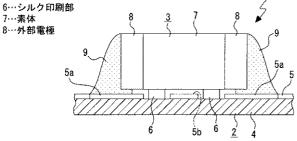

第1の変形例に係る回路基板1Aは、例えば、積層セラミックコンデンサー3の素体7と絶縁基板4の間に回路パターン5の一部(銅箔)5aが形成されている場合に、この一部5aをエッチングによって除去することにより離隔空間10を形成した例である(図4参照)。

### [0061]

回路基板1Aのように離隔空間10が形成されていることにより、積層セラミックコンデンサー3に振動が生じても素体7が絶縁基板4(配線板2)に接触し難い状態にされている。従って、離隔空間10は、積層セラミックコンデンサー3に電圧の印加に伴う電歪効果が生じたときに、素体7と配線板2の接触を抑制する接触抑制部として機能し、接触抑制部によって可聴域の音が出力される鳴きの発生が抑制される。

### [0062]

このように素体 7 と配線板 2 の接触を抑制する接触抑制部として離隔空間 1 0 が形成されている場合においても、積層セラミックコンデンサー 3 の加工や構造の変更を必要とせず積層セラミックコンデンサー 3 の配線板 2 に対する実装位置も制約されないため、製造コストの高騰及び設計の自由度の低下を来たすことなく鳴きの発生を抑制することができる。

#### [0063]

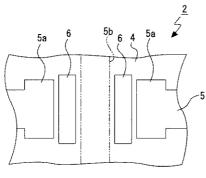

第2の変形例に係る回路基板1Bは、例えば、積層セラミックコンデンサー3の素体7と絶縁基板4の間に回路パターン5の一部(銅箔)5aが形成されている場合に、この一部5aをエッチングによって除去することにより離隔空間11を形成し、加えて、シルク印刷部6、6を設けた例である(図5参照)。

20

10

30

40

### [0064]

回路基板1Bのように離隔空間11が形成され、加えて、シルク印刷部6、6が設けられていることにより、積層セラミックコンデンサー3に振動が生じても素体7が絶縁基板4(配線板2)に接触し難い状態にされている。従って、離隔空間11及びシルク印刷部6、6は、積層セラミックコンデンサー3に電圧の印加に伴う電歪効果が生じたときに、素体7と配線板2の接触を抑制する接触抑制部として機能し、接触抑制部によって可聴域の音が出力される鳴きの発生が抑制される。

### [0065]

このように素体 7 と配線板 2 の接触を抑制する接触抑制部として離隔空間 1 1 及びシルク印刷部 6、6が形成されている場合においても、積層セラミックコンデンサー 3 の加工や構造の変更を必要とせず積層セラミックコンデンサー 3 の配線板 2 に対する実装位置も制約されないため、製造コストの高騰及び設計の自由度の低下を来たすことなく鳴きの発生を抑制することができる。

### [0066]

特に、第1の変形例及び第2の変形例に係る回路基板1A、1Bにおけるエッチングによる銅箔の除去は、回路基板1A、1Bの製造時におけるエッチング工程と同じ製造工程において行うことができ、製造工程の追加を必要とせず、その分、製造コストの高騰や製造時間の増大を来たすことなく鳴きの発生を抑制することができる。

### [0067]

[本技術]

本技術は、以下のような構成とすることもできる。

#### [0068]

(1)複数の誘電体層と複数の内部電極とが交互に積層された素体の両端部に前記内部電極が接続された一対の外部電極が設けられた積層セラミックコンデンサーと、絶縁基板と前記絶縁基板上に銅箔によって形成され前記積層セラミックコンデンサーの一対の外部電極がそれぞれ接続される一対のランドとを有する配線板とを備え、前記配線板における前記一対のランド間に前記積層セラミックコンデンサーの素体と前記配線板の接触を抑制する接触抑制部を設けた回路基板。

## [0069]

(2)前記接触抑制部として、前記絶縁基板上にシルク印刷部を設けた前記(1)に記載の回路基板。

#### [0070]

(3)前記シルク印刷部を前記一対のランドの並び方向に離隔して二つ設けた前記(2)に記載の回路基板。

### [0071]

(4)前記接触抑制部として、前記積層セラミックコンデンサーの素体と前記絶縁基板の間の前記銅箔をエッチングによって除去することにより離隔空間を形成した前記(1)から前記(3)の何れかに記載の回路基板。

### [0072]

(5)前記接触抑制部として、前記絶縁基板上に設けたシルク印刷部と、前記積層セラミックコンデンサーの素体と前記絶縁基板の間の前記銅箔をエッチングによって除去することにより離隔空間とを形成した前記(1)から前記(4)の何れかに記載の回路基板。

### [0073]

上記した技術を実施するための最良の形態において示した各部の具体的な形状及び構造は、何れも本技術を実施する際の具体化のほんの一例を示したものにすぎず、これらによって本技術の技術的範囲が限定的に解釈されることがあってはならないものである。

### 【図面の簡単な説明】

### [0074]

【図1】図2乃至図5と共に本技術回路基板の最良の形態を示すものであり、本図は、一部を断面にして示す拡大側面図である。

10

20

30

40

- 【図2】配線板の拡大平面図である。

- 【図3】音圧レベルの測定値を示すグラフ図である。

- 【図4】第1の変形例を一部を断面にして示す拡大側面図である。

- 【図5】第2の変形例を一部を断面にして示す拡大側面図である。

### 【符号の説明】

### [0075]

1 ... 回路基板、 2 ... 配線板、 3 ... 積層セラミックコンデンサー、 4 ... 絶縁基板、 5 a ... ランド、6…シルク印刷部、7…素体、8…外部電極、1A…回路基板、1B…回路基板 、10…離隔空間、11…離隔空間

## 【図1】

- 1…回路基板

- 2…配線板

- 3…積層セラミックコンデンサー

- 4…絶縁基板 5a…ランド

- 7…素体 8…外部電極

# 【図2】

- 2…配線板 4…絶縁基板

- 5a…ランド 6…シルク印刷部

### 【図3】

# 【図4】

1A…回路基板 2…配線板 3…積層セラミックコンデンサー 4…絶縁基板 7…素体 8…外部電極 10…離隔空間 10

# 【図5】

1B…回路基板